一个网站是如何建设龙岗做网站公司szaow

第三章:负载均衡中的负载算法

负载算法分为静态的和动态的。静态的连接分布模式是预先设置的,流量处理中是不会变化的,动态的连接分布模式也是预先设置的,但是连接分布会根据某些因素的改变而调整。

轮询(round robin):

将新建的链接逐一转发到每一个后端服务器上。静态的。

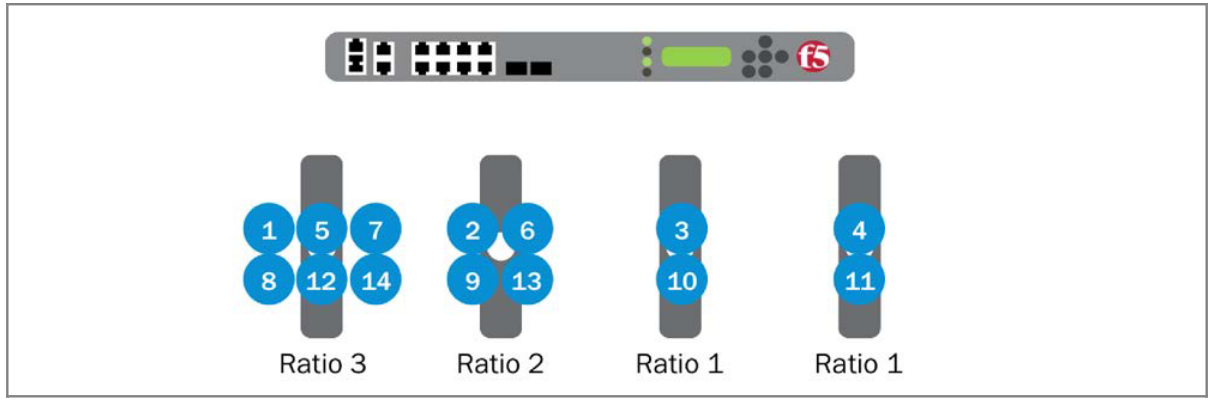

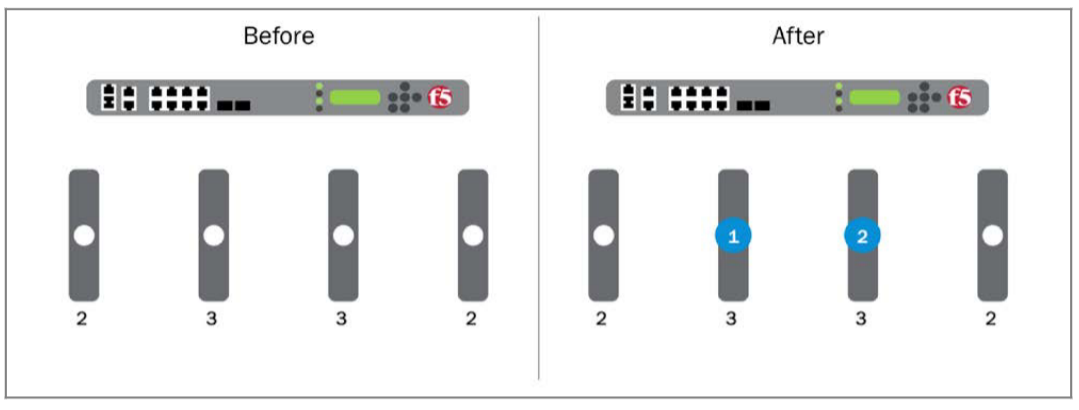

比率轮询(ratio):

可以根据赋予的权重将流量分不到后端服务器上,ratio可以根据member或者node为单位进行赋予。静态的。

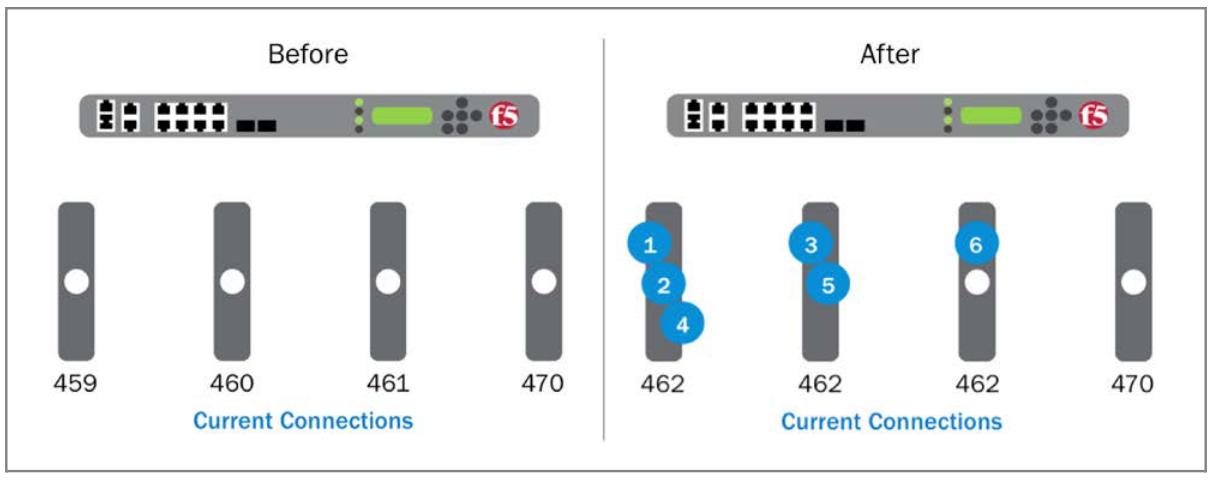

最小连接数(least connnection):

将新建的链接分发到当前连接最少的后端。对于长连接场景有很好的均衡效果,随着时间推移,设备的连接数会比较均匀。

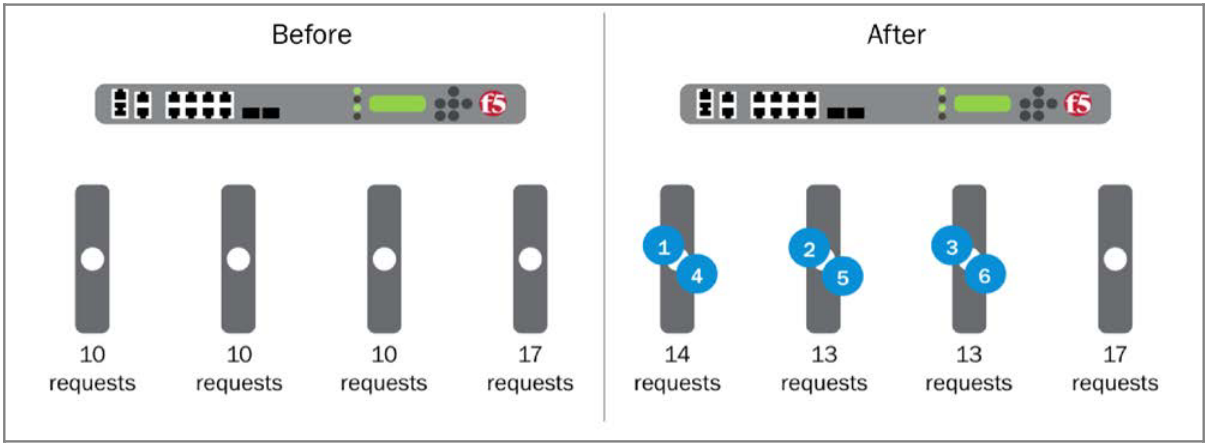

最快(fastest):

将新连接分配给当前拥有最少未完成的第7层请求的应用节点,如果关联的vs同时不具备tcp和7层的profile,就会使用最少连接算法,进行负载。此方式对于流量分配到响应时间可能不同的设备非常有用。

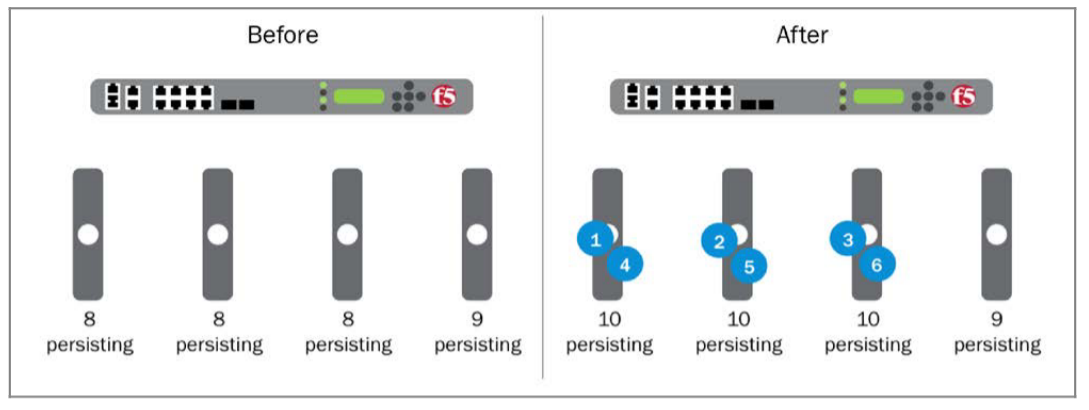

最少会话(least sessions):

将新建连接转发到持久化表中最少记录的后端服务器上,这种方式必须关联persistence的profile,且persistence的profile必须使用持久化表。

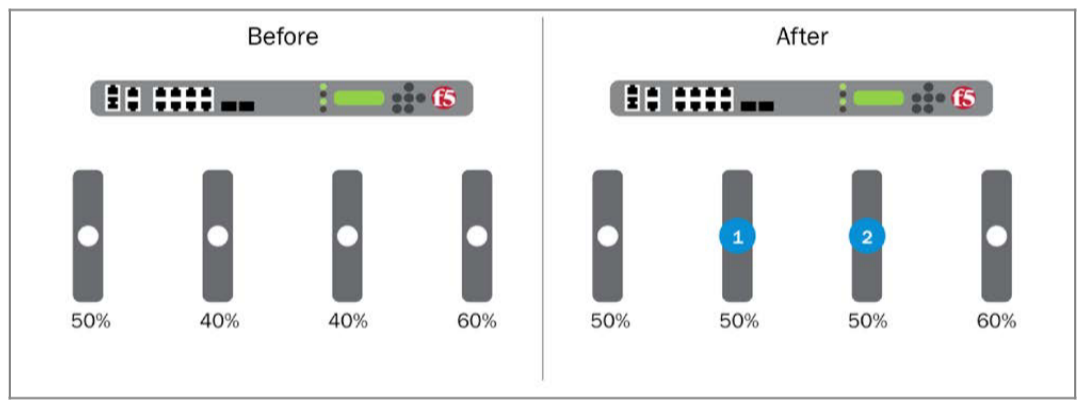

加权最少连接数(weight least connection):

要求每个成员或节点分配一个非零连接限制,然后,请求被分配到使用其容量的最小百分比设备,其中容量是当前连接数与允许的最大连接数的比率。

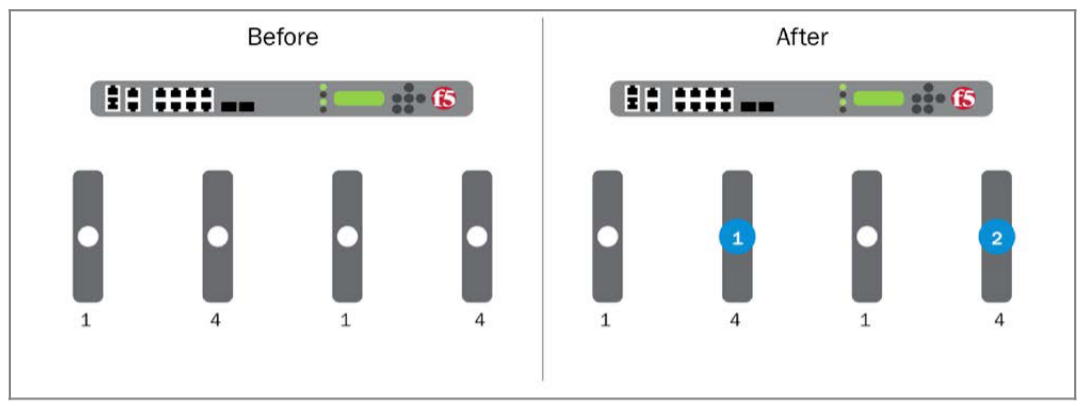

观察(observed):

此算法计算一个动态比率(ratio)值,这个值基于四层连接数,bigip系统每秒钟都会统计每个后端的连接数,并分配一个比率值,当有一个新连接,会根据分配的比率值来进行连接分配,优选比率值最大的后端。

预测(predictive):

该算法对服务器性能随时间的推移进行排名,并优选性能有所提高的后端服务器,bigip系统根据一段时间内到每个成员的四层连接数计算动态比率值,每秒钟,bigip系统会观察到每个后端服务器的四层连接数,并与之前的连接数进行对比,以确定性能趋势,并为每一个成员分配一个比率值,如果连接数保持不变,则系统不更改比率值,如果连接数增加,则比率值减少,反之增加,新建连接会根据比率值进行分配,优选比率值最大的后端服务器。

动态比率(dynamic ratio):

此算法专门用于RealNetwork RealSystem服务器平台,配置了windows management instrumentation的windows平台或者配置了snmp代理的服务器。

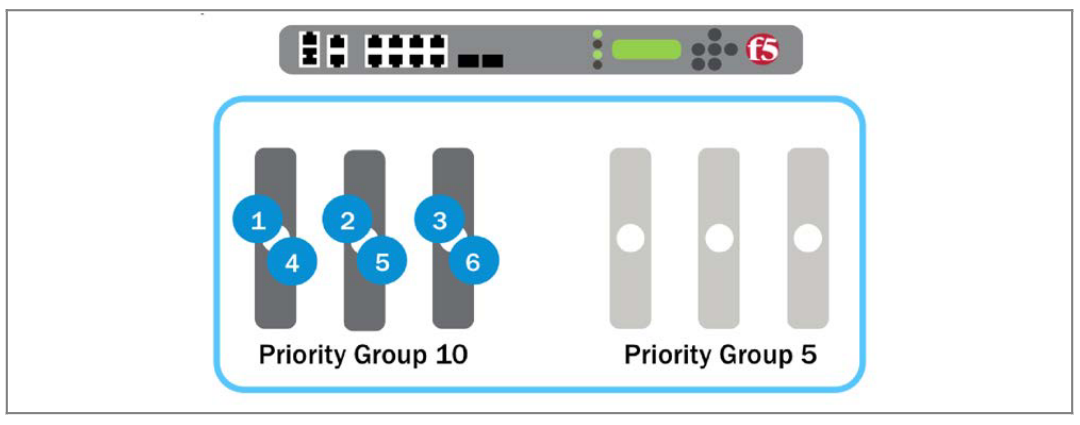

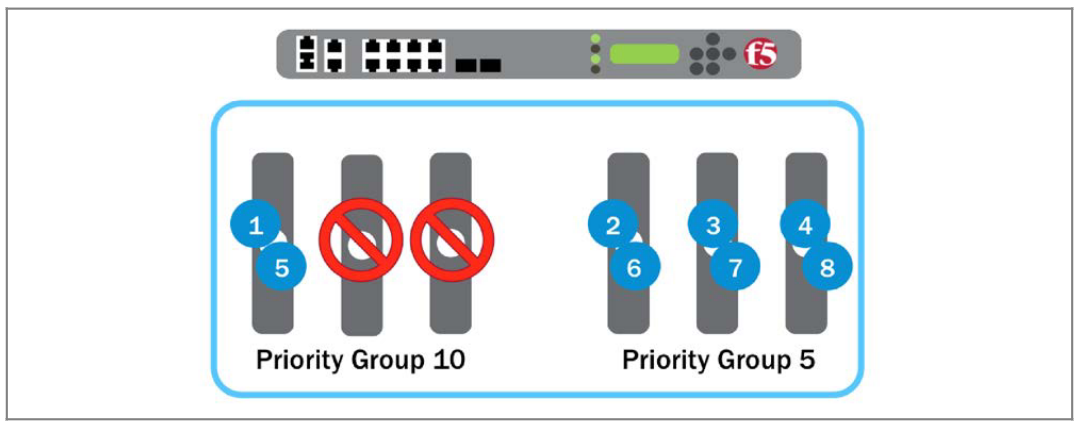

优先组(priority group ):

优先组的概念允许你在单个池子内定于主要成员和备用成员。你需要对组进行赋值,同时要配置这个组最小成员数,当小于可用成员小于这个数的时候,会启用备用组。

举个例子:一个pool有6个member。3个在组10,3个在组5,同时配置最少可用成员为2,当接收到流量的时候,只有组10的3个成员会收到流量,组5的三个成员不会被分配流量。

如果此时组10内的两个成员健康检测失败或者手工配置为不可用,bigip系统将会激活下一个低优先级的组,这里就是组5的三个成员,此时流量将会分配到4个后端服务器上。

一般优先组使用有两种场景,第一种,在主用出现大量故障的情况时,需要启用道歉服务器。第二种,如果后端服务器被多种业务使用,比如同一个服务器同时具备web和ftp程序,正常时候服务器承载ftp,如果优先组的web服务器大量故障,承载了ftp的服务器被激活,也可以充当web服务器。

优先组取值范围:0-4294967295。

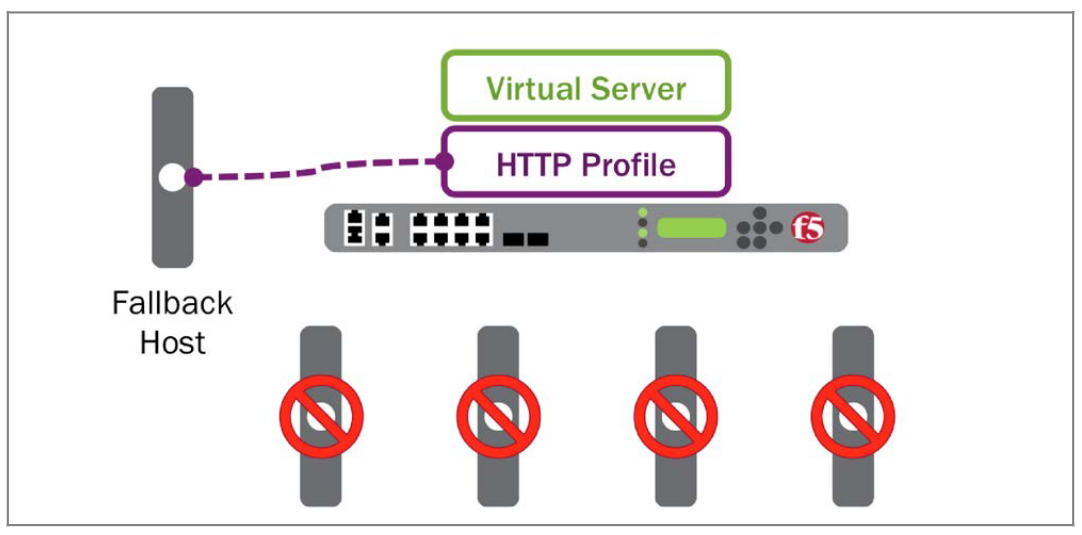

备用主机( fallback host):

如果池中的成员都不能正常提供服务了,vs将会直接发送一个http回应报文到客户端,将他们重定向到其他的主机上,比如道歉服务器,备用主机的能力是在http profile中配置,且只能应用在http场景里。

实验:

配置优先组:

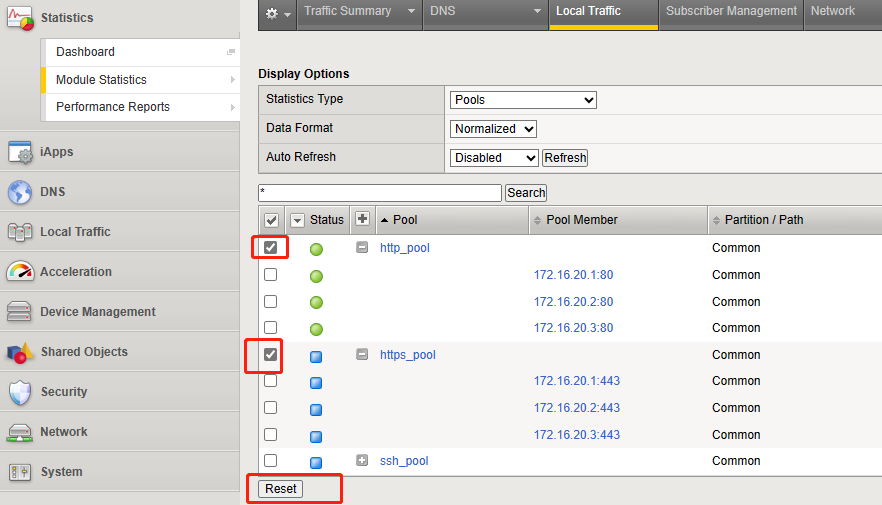

1、清除http_pool的统计值

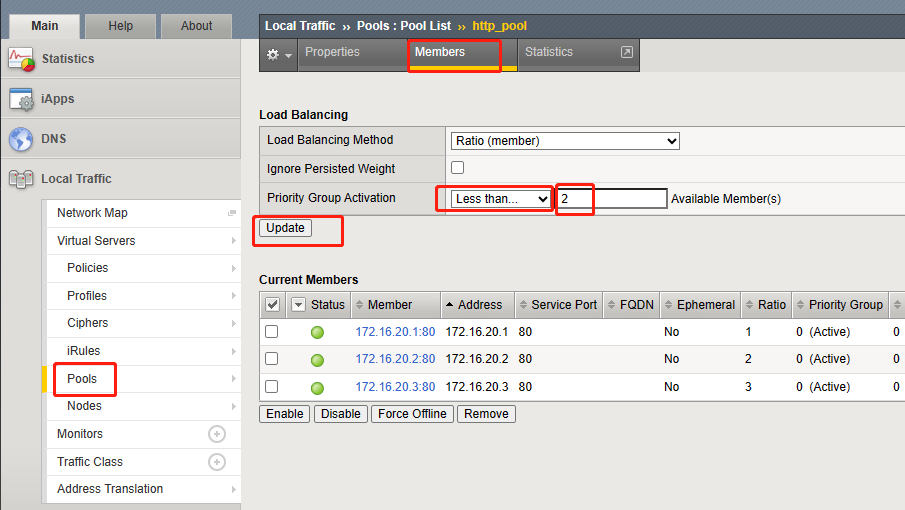

2、给http_pool配置少于2个成员时候,激活优先组

- 路径:Local Traffic ›› Pools : Pool List ›› http_pool,member tab ›› Priority Group Activation

- tmsh:

modify ltm pool http_pool min-active-members 2

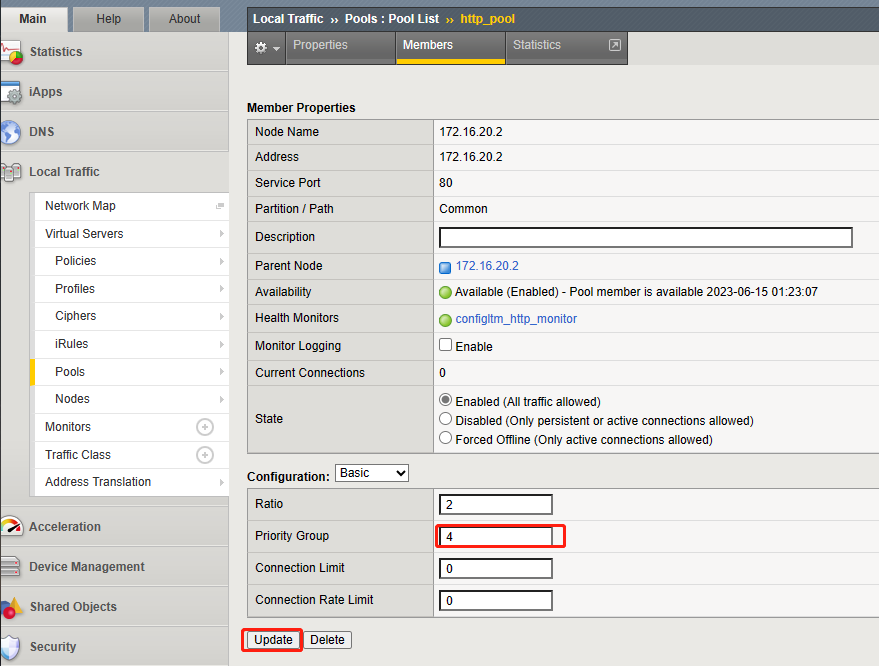

3、更改http_pool的所属组

| memebr | ratio | priority group |

|---|---|---|

| 172.16.20.1:80 | 1 | 0 |

| 172.16.20.2:80 | 2 | 4 |

| 172.16.20.3:80 | 3 | 4 |

- 路径:Local Traffic ›› Pools : Pool List ›› http_pool ›› Current Members

- tmsh:

modify ltm pool http_pool members modify { 172.16.20.2:http { priority-group 4 } }

modify ltm pool http_pool members modify { 172.16.20.3:http { priority-group 4 } }

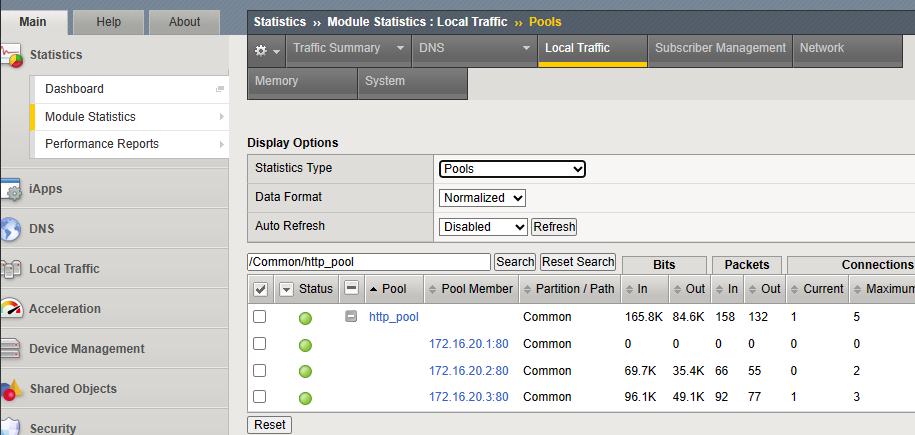

4、在浏览器中输入10.10.10.100,刷新10次,看统计信息。

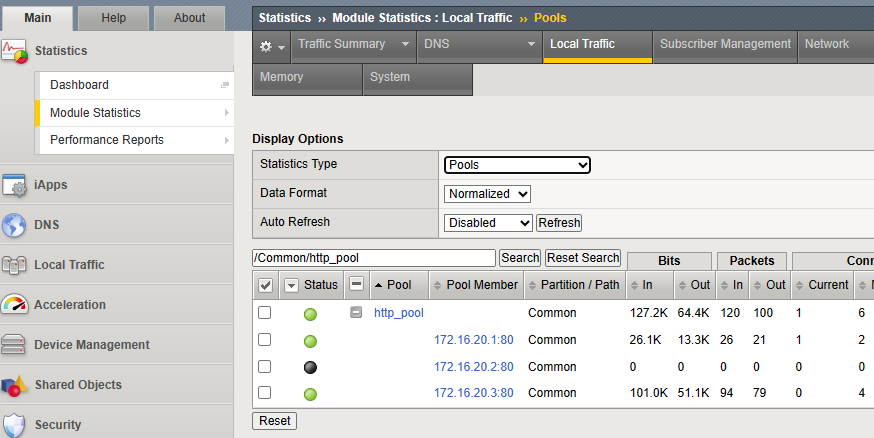

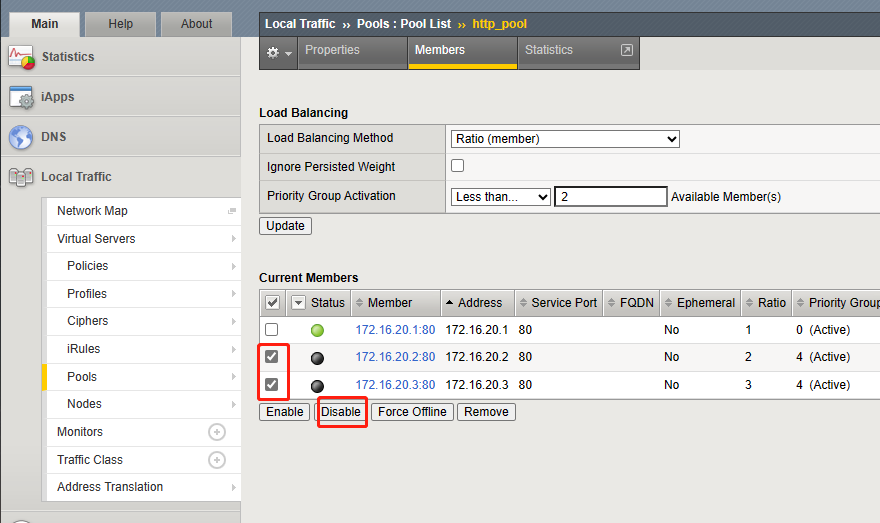

5、清除http_pool的统计值,并把172.16.20.2:80这个rs配置为disable,在浏览器中输入10.10.10.100,刷新10次,看统计信息。

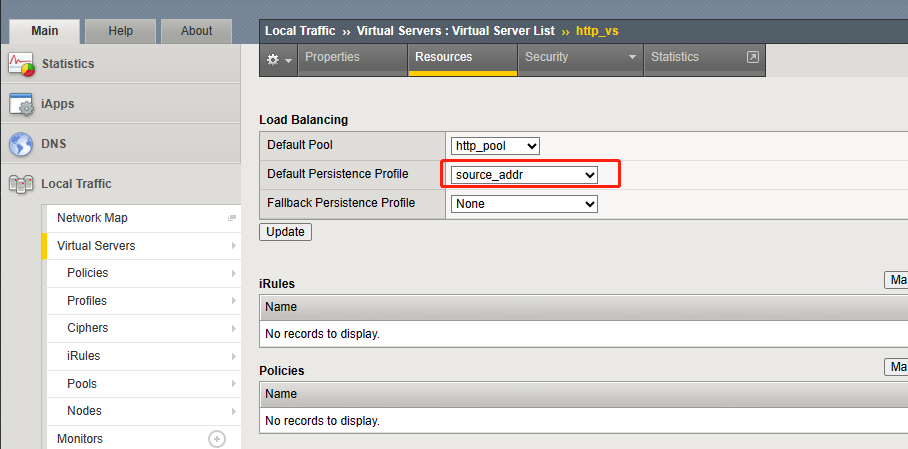

6、将172.16.20.3:80这个rs配置为disable,确保流量完全打到172.16.20.1这台机器上,并给http_vs添加基于source_addr的持久化配置。在浏览器中输入10.10.10.100并刷新10次。此时在将172.16.20.2和3配置成enable,在浏览器中请求10.10.10.100,看数据流达到那台rs上。

7、删除http_vs的持久化配置

实验预期:

将优先级组激活设置为少于2个成员并启用所有池成员,172.16.20.1:80应该没有收到流量。流量以2:3的比例分配给成员172.16.20.2和172.16.20.3。

如果将优先级组激活设置为少于2个成员,并且禁用池成员172.16.20.2:80,则激活下一个较低优先级组(0)。然后将流量按1:3的比例分配给成员172.16.20.1和172.16.20.3。

当向http_vs添加源地址关联持久性配置文件,并强制连接进行负载平衡并持久化到最低优先级组(172.16.20.1:80)中的池成员时,即使在重新启用其他两个成员并且池中再次有两个成员可用之后,仍然持久化到172.16.20.1:80,并且将继续这样转发,直到持久性记录过期。

配置比率负载均衡:

将负载均衡算法从Ratio(member)调整成为Ratio(node),调整node节点172.16.20.3的权重为5.

2、在网页中请求10.10.10.100,刷新10次,查看http_pool的统计值,

实验预期:

由于优先级组仍然在http_pool上配置,因此只需激活两个池成员即可满足最小值。成员172.16.20.2:80和172.16.20.3:80在最高优先级组中,并且是BIG-IP系统负载平衡连接的唯一成员。但是,即使池成员172.16.20.2:80的比率为2,池成员172.16.20.3:80的比率为3,BIG-IP系统也会忽略这些比率,而使用关联节点上配置的比率。节点172.16.20.3的比值为5,节点172.16.20.2的比值为1。因此,地址172.16.20.3:80的连接数大约是地址172.16.20.2:80的连接数的5倍.

测试连接限制对优先组激活的影响

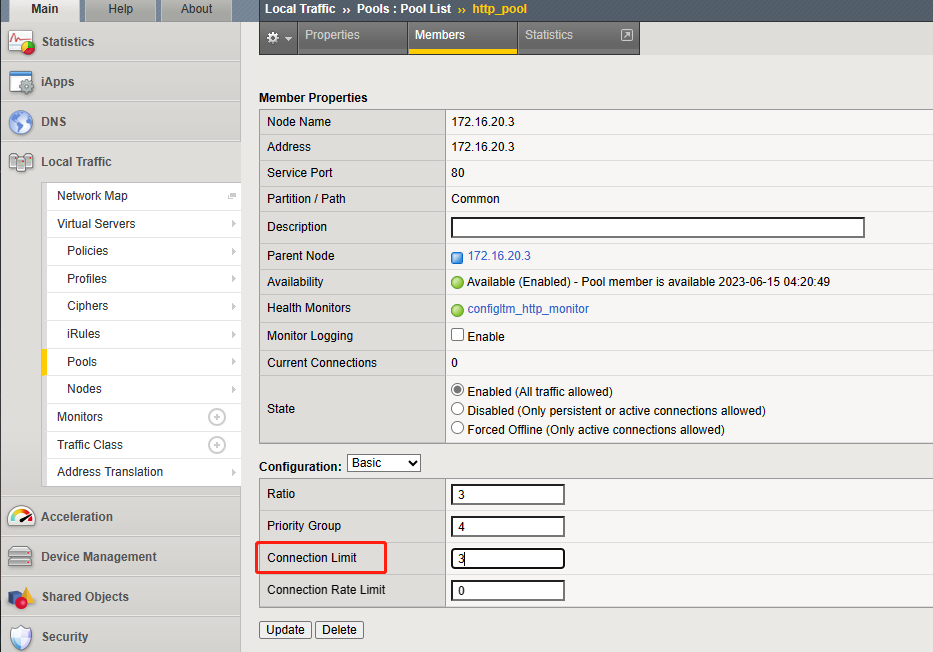

1、清除http_pool的统计值,调整172.16.20.3:80的connection limit值为3.

2、在浏览器中请求10.10.10.100多次。

3、查看统计值。

4、调整http_pool的算法为轮询算法,并关闭优先组。

5、设置172.16.20.3:80的connection limit值为0

6、调整http_pool的成员,优先组的数值为0,ratio均为1.

实验预期:

在对池成员172.16.20.3:80设置连接限制之前,流量只在优先级组4中的两个成员172.16.20.2:80和172.16.20.3:80之间进行负载分担。到池成员172.16.20.3:80的最大并发连接数远远超过3。

在将池成员172.16.20.3:80的连接限制设置为3后,流量在所有池成员之间进行负载均衡,因为该池成员将周期性地达到其最大连接数,从而触发激活优先级组0,其中172.16.20.1:80是其成员。激活后,BIG-IP系统在所有三个池成员之间负载均衡流量,直到172.16.20.3:80上的连接数低于3。当查看http_pool的统计信息时,到172.16.20.3:80的最大并发连接数应该是3。到其他池成员的最大并发连接数将可能比3大。