西红门做网站又一地发现2例阳性

末尾获取源码

开发语言:Java

Java开发工具:JDK1.8

后端框架:SSM

前端:采用Vue技术开发

数据库:MySQL5.7和Navicat管理工具结合

服务器:Tomcat8.5

开发软件:IDEA / Eclipse

是否Maven项目:是

目录

一、项目简介

二、主要工作

三、系统项目截图

3.1管理员功能

3.2用户功能

3.3商家功能

四、核心代码

4.1登录相关

4.2文件上传

4.3封装

一、项目简介

21世纪的今天,随着社会的不断发展与进步,人们对于信息科学化的认识,已由低层次向高层次发展,由原来的感性认识向理性认识提高,管理工作的重要性已逐渐被人们所认识,科学化的管理,使信息存储达到准确、快速、完善,并能提高工作管理效率,促进其发展。

论文主要是对绿色农产品推广应用网站进行了介绍,包括研究的现状,还有涉及的开发背景,然后还对系统的设计目标进行了论述,还有系统的需求,以及整个的设计方案,对系统的设计以及实现,也都论述的比较细致,最后对绿色农产品推广应用网站进行了一些具体测试。

本文以Java为开发技术,实现了一个绿色农产品推广应用网站。绿色农产品推广应用网站的主要实现功能包括:管理员:首页、个人中心、用户管理、商家管理、农业行情管理、农业技巧管理、商品类型管理、商品信息管理、商品购买管理、交流信息管理、交流回复管理、留言板管理、系统管理,商家;首页、个人中心、商品类型管理、商品信息管理、商品购买管理、交流信息管理、交流回复管理,用户;首页、个人中心、商品购买管理、交流信息管理、交流回复管理、留言板管理、我的收藏管理,前台首页;首页、农业行情、农业技巧、商品信息、农业资讯、留言反馈、个人中心、后台管理功能,基本上实现了整个绿色农产品推广应用网站的过程。

具体在系统设计上,采用了B/S的结构,同时,也使用Java技术在动态页面上进行了设计,后台上采用Mysql数据库,是一个非常优秀的绿色农产品推广应用网站。

二、主要工作

一开始,本文就对系统内谈到的基本知识,从整体上进行了描述,并在此基础上进行了系统分析。为了能够使本系统较好、较为完善的被设计实现出来,就必须先进行分析调查。基于之前相关的基础,在功能上,对新系统进行了细致的分析。然后通过详细的分析,进行系统设计,其次,系统在实施的可行性上,我选择了Java技术来进行开发设计,在数据存储上,采用 Mysql数据库来进行设计。由于Java和Mysql都已经非常成熟,因此无论在各个方面,都非常可靠安全实用。最后对系统进行测试完善并发布。

三、系统项目截图

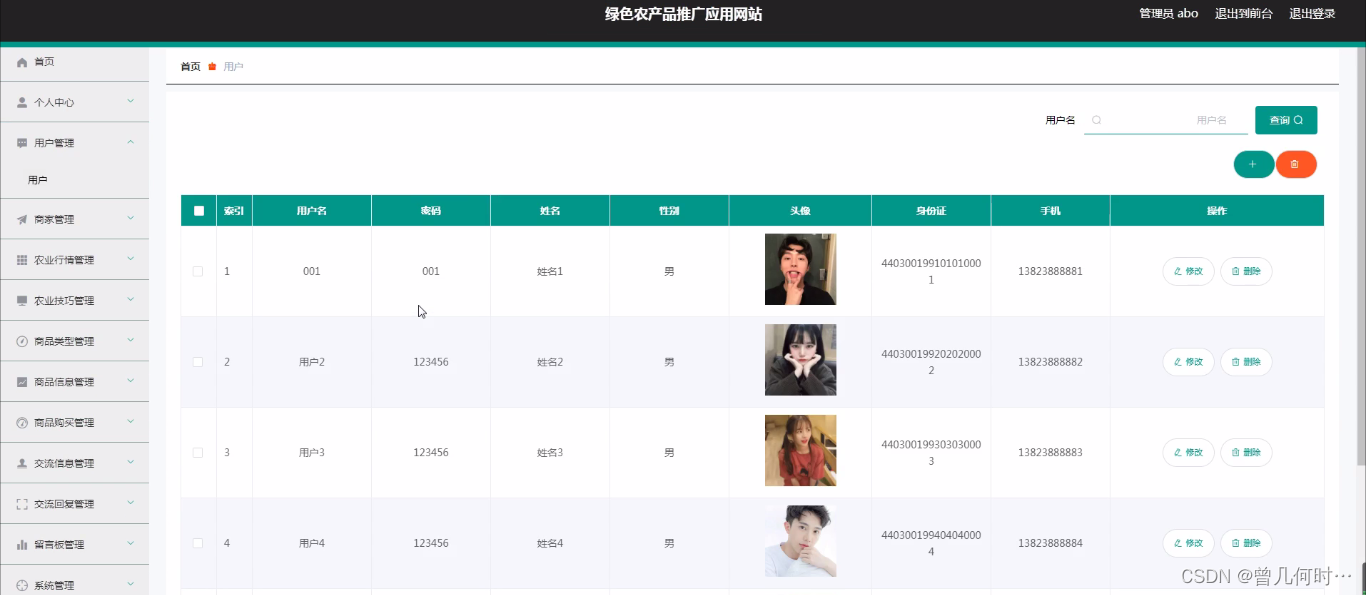

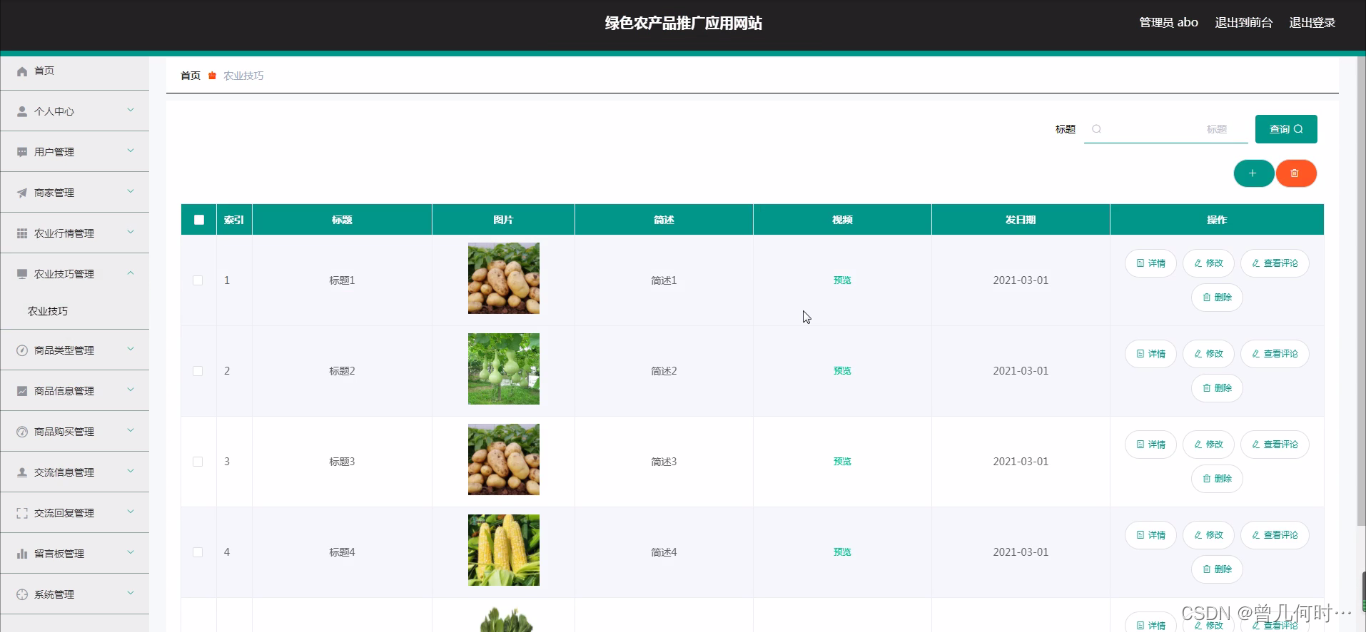

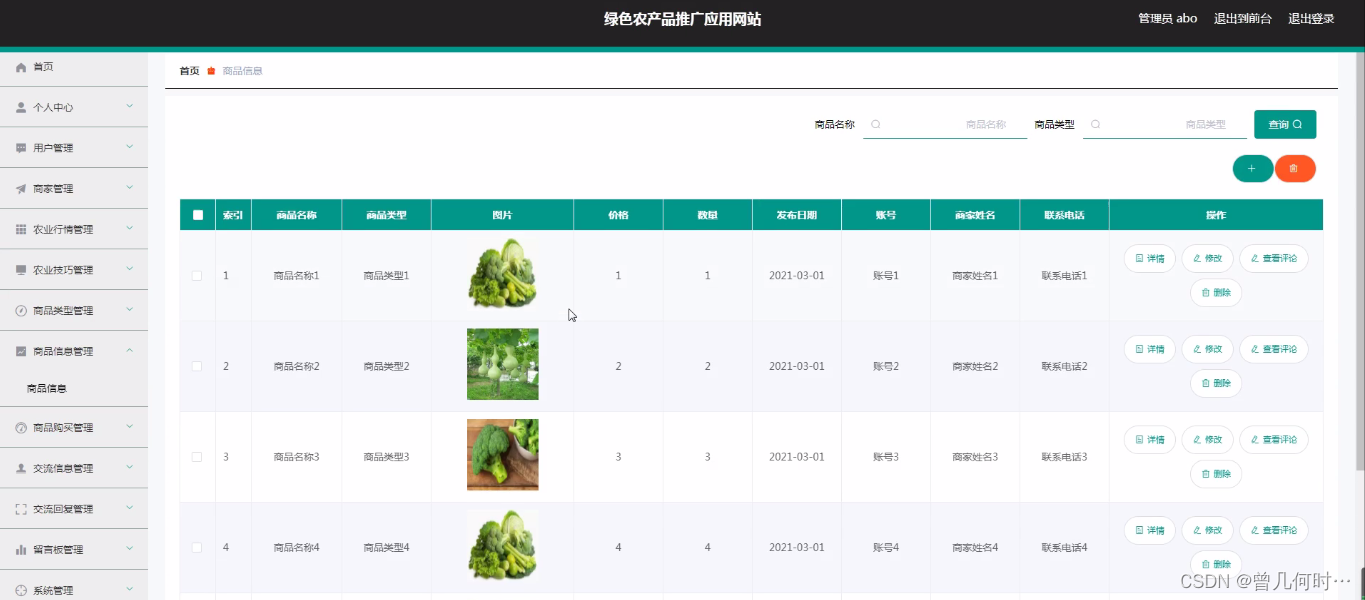

3.1管理员功能

管理员输入个人的账号、密码和角色登录系统,这时候系统的数据库就会在进行查找相关的信息,如果我们输入的账号、密码和角色不正确,数据库就会提示出错误的信息提示,同时会提示管理员重新输入自己的账号、密码,直到账号密码输入成功后,会提登录成功的信息。

管理员对用户管理进行编辑填写用户名、密码、姓名、性别、头像、身份证、手机 并进行详情、删除、修改等操作。

管理员对商家管理进行编辑账号、密码、商家姓名、性别、头像、身份证、联系电话等信息并可以进行详情、删除、修改操作。

管理员对农业技巧管理进行编辑标题、图片、简述、视频、发布日期等信息并可以进行详情、删除、修改操作。

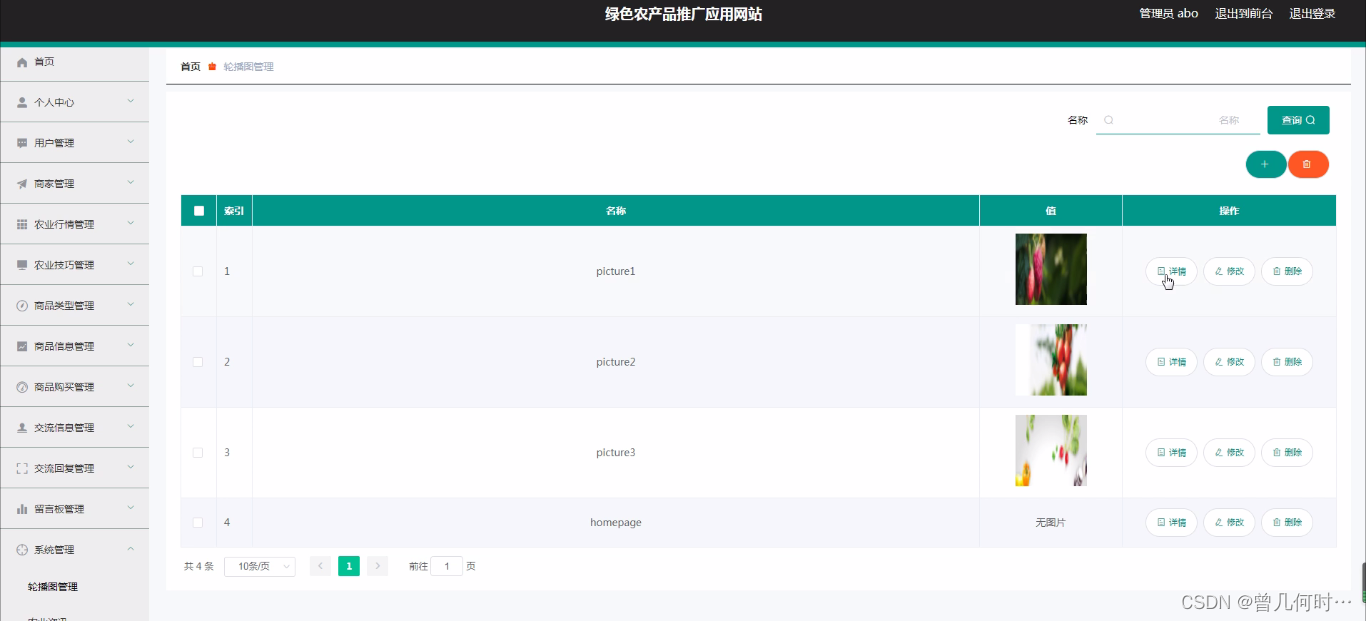

轮播图;该页面为轮播图管理界面。管理员可以在此页面进行首页轮播图的管理,通过新建操作可在轮播图中加入新的图片,还可以对以上传的图片进行修改操作,以及图片的删除操作。

管理员对商品信息管理进行填写商品名称、商品类型、图片、价格、数量、发布日期、账号、商家姓名、联系电话等信息进行详情、删除、修改操作。

管理员对交流信息管理进行编辑标题、账号、商家姓名、日期、用户名、姓名等信息并可以进行详情、删除、修改操作。

管理员对交流回复管理进行编辑标题、用户名、姓名、回复日期、账号、商家姓名等信息并可以进行详情、删除、修改操作。

3.2用户功能

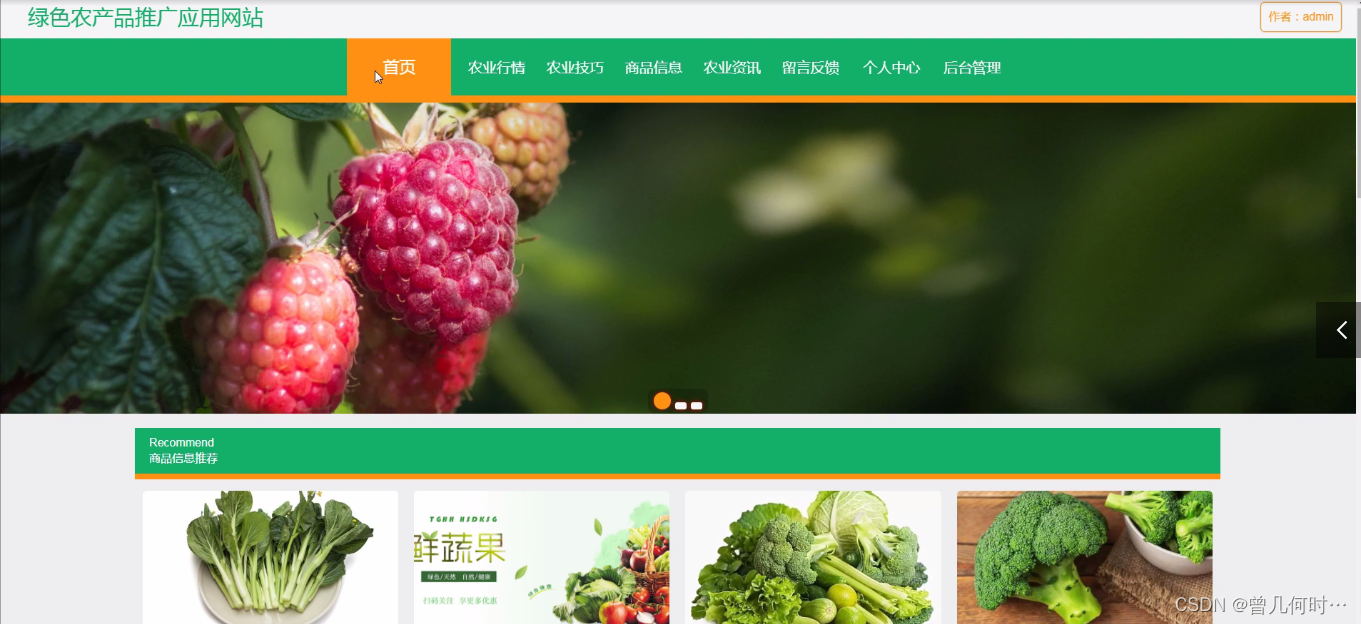

前台首页详情页面:首页、农业行情、农业技巧、商品信息、农业资讯、留言反馈、个人中心、后台管理等功能操作。

用户在线填写账号、密码等信息进行登录操作。

用户进入商品信息可以填写商品名称、商品类型、图片、价格、数量、发布日期、账号、商家姓名、联系电话、点击次数等信息,并可以进行购买、咨询操作。

用户进入商品信息可以填写商品名称、商品类型、图片、价格、数量、发布日期、账号、商家姓名、联系电话、点击次数等信息,并可以进行购买、咨询操作。

用户进入留言反馈可以填写留言内容进行立即提交操作。

用户进入商品购买管理可以查看订单编号、商品名称、商品类型、账号、价格、数量、总价格、购买日期、用户名、姓名、手机、地址、是否支付等信息进行详情、删除。

用户进入留言板管理可以填写用户名、留言内容、回复内容并可以进行详情、删除等操作。

用户进入留言板管理可以填写用户名、留言内容、回复内容并可以进行详情、删除等操作。

用户进入我的收藏管理可以填写收藏名称、收藏图片等信息,并可以进行详情、删除等操作。

3.3商家功能

3.3商家功能

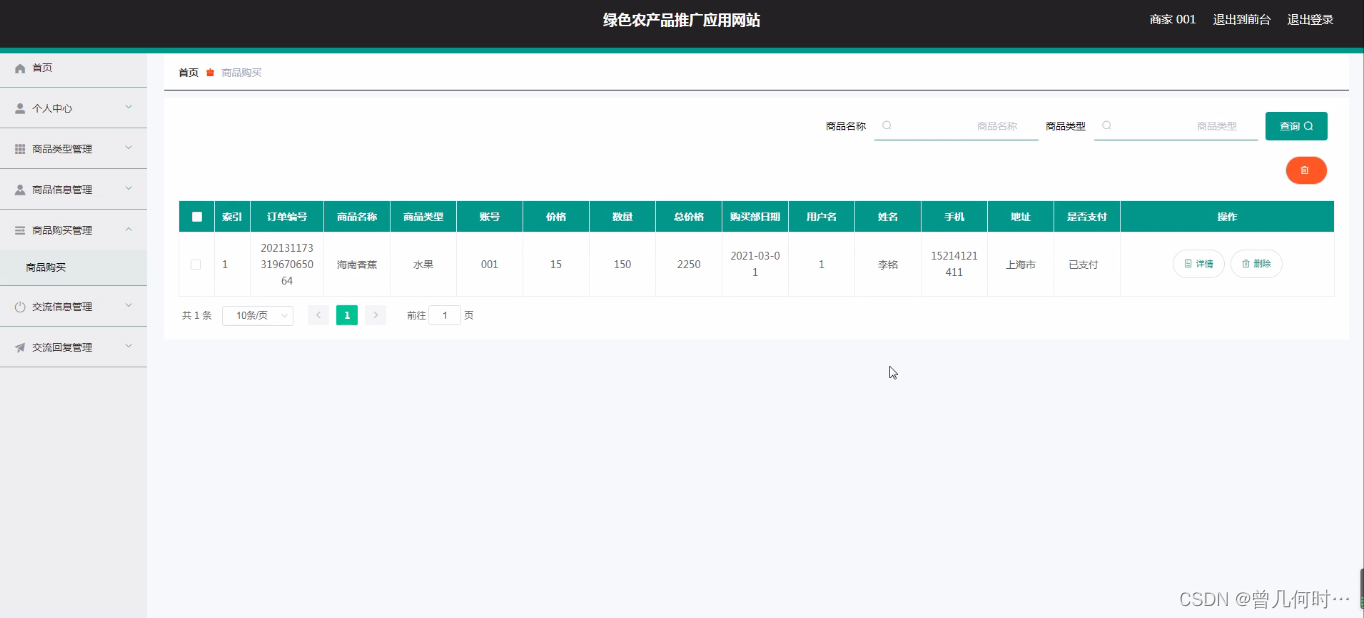

商家进入商品购买管理可以查看订单编号、商品名称、商品类型、账号、价格、数量、总价格、购买日期、用户名、姓名、手机、地址、是否支付等信息,并可以进行详情、删除等操作。

商家进入交流信息管理可以查看标题、账号、商家姓名、日期、用户名、姓名等信息,进行删除、详情等操作。

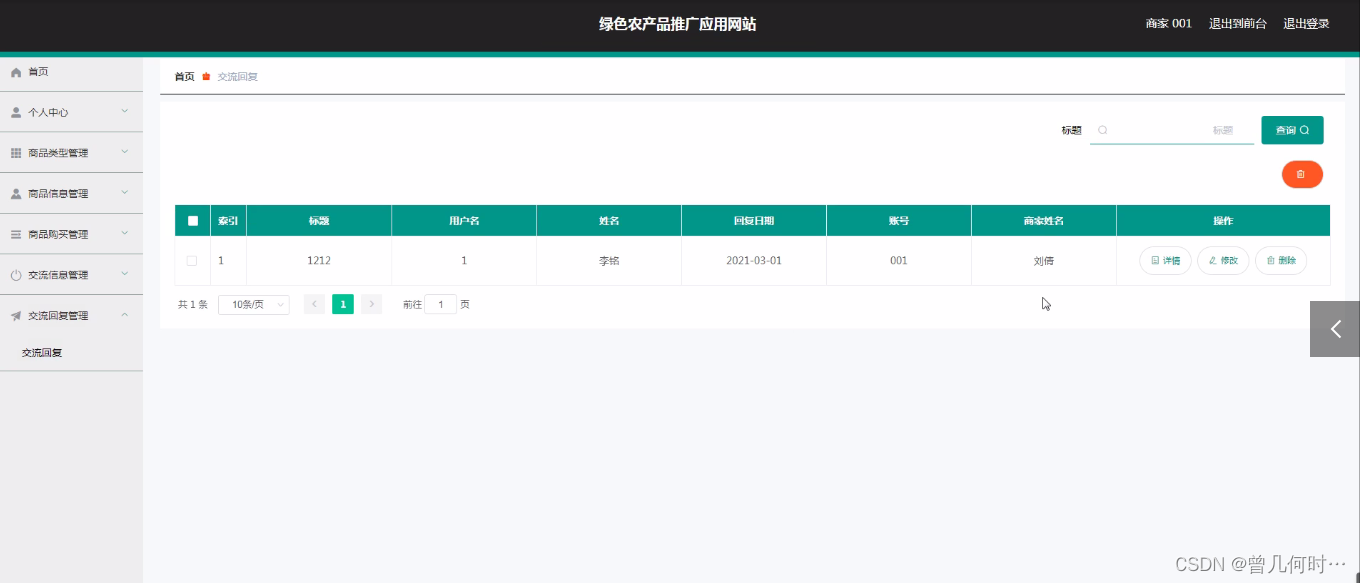

商家进入交流回复管理可以查看标题、用户名、姓名、回复日期、账号、商家姓名等信息,详情、删除等操作。

四、核心代码

4.1登录相关

package com.controller;import java.util.Arrays;

import java.util.Calendar;

import java.util.Date;

import java.util.Map;import javax.servlet.http.HttpServletRequest;import org.springframework.beans.factory.annotation.Autowired;

import org.springframework.stereotype.Controller;

import org.springframework.web.bind.annotation.GetMapping;

import org.springframework.web.bind.annotation.PathVariable;

import org.springframework.web.bind.annotation.PostMapping;

import org.springframework.web.bind.annotation.RequestBody;

import org.springframework.web.bind.annotation.RequestMapping;

import org.springframework.web.bind.annotation.RequestParam;

import org.springframework.web.bind.annotation.ResponseBody;

import org.springframework.web.bind.annotation.RestController;import com.annotation.IgnoreAuth;

import com.baomidou.mybatisplus.mapper.EntityWrapper;

import com.entity.TokenEntity;

import com.entity.UserEntity;

import com.service.TokenService;

import com.service.UserService;

import com.utils.CommonUtil;

import com.utils.MD5Util;

import com.utils.MPUtil;

import com.utils.PageUtils;

import com.utils.R;

import com.utils.ValidatorUtils;/*** 登录相关*/

@RequestMapping("users")

@RestController

public class UserController{@Autowiredprivate UserService userService;@Autowiredprivate TokenService tokenService;/*** 登录*/@IgnoreAuth@PostMapping(value = "/login")public R login(String username, String password, String captcha, HttpServletRequest request) {UserEntity user = userService.selectOne(new EntityWrapper<UserEntity>().eq("username", username));if(user==null || !user.getPassword().equals(password)) {return R.error("账号或密码不正确");}String token = tokenService.generateToken(user.getId(),username, "users", user.getRole());return R.ok().put("token", token);}/*** 注册*/@IgnoreAuth@PostMapping(value = "/register")public R register(@RequestBody UserEntity user){

// ValidatorUtils.validateEntity(user);if(userService.selectOne(new EntityWrapper<UserEntity>().eq("username", user.getUsername())) !=null) {return R.error("用户已存在");}userService.insert(user);return R.ok();}/*** 退出*/@GetMapping(value = "logout")public R logout(HttpServletRequest request) {request.getSession().invalidate();return R.ok("退出成功");}/*** 密码重置*/@IgnoreAuth@RequestMapping(value = "/resetPass")public R resetPass(String username, HttpServletRequest request){UserEntity user = userService.selectOne(new EntityWrapper<UserEntity>().eq("username", username));if(user==null) {return R.error("账号不存在");}user.setPassword("123456");userService.update(user,null);return R.ok("密码已重置为:123456");}/*** 列表*/@RequestMapping("/page")public R page(@RequestParam Map<String, Object> params,UserEntity user){EntityWrapper<UserEntity> ew = new EntityWrapper<UserEntity>();PageUtils page = userService.queryPage(params, MPUtil.sort(MPUtil.between(MPUtil.allLike(ew, user), params), params));return R.ok().put("data", page);}/*** 列表*/@RequestMapping("/list")public R list( UserEntity user){EntityWrapper<UserEntity> ew = new EntityWrapper<UserEntity>();ew.allEq(MPUtil.allEQMapPre( user, "user")); return R.ok().put("data", userService.selectListView(ew));}/*** 信息*/@RequestMapping("/info/{id}")public R info(@PathVariable("id") String id){UserEntity user = userService.selectById(id);return R.ok().put("data", user);}/*** 获取用户的session用户信息*/@RequestMapping("/session")public R getCurrUser(HttpServletRequest request){Long id = (Long)request.getSession().getAttribute("userId");UserEntity user = userService.selectById(id);return R.ok().put("data", user);}/*** 保存*/@PostMapping("/save")public R save(@RequestBody UserEntity user){

// ValidatorUtils.validateEntity(user);if(userService.selectOne(new EntityWrapper<UserEntity>().eq("username", user.getUsername())) !=null) {return R.error("用户已存在");}userService.insert(user);return R.ok();}/*** 修改*/@RequestMapping("/update")public R update(@RequestBody UserEntity user){

// ValidatorUtils.validateEntity(user);userService.updateById(user);//全部更新return R.ok();}/*** 删除*/@RequestMapping("/delete")public R delete(@RequestBody Long[] ids){userService.deleteBatchIds(Arrays.asList(ids));return R.ok();}

}

4.2文件上传

package com.controller;import java.io.File;

import java.io.FileNotFoundException;

import java.io.IOException;

import java.util.Arrays;

import java.util.Date;

import java.util.HashMap;

import java.util.List;

import java.util.Map;

import java.util.Random;

import java.util.UUID;import org.apache.commons.io.FileUtils;

import org.apache.commons.lang3.StringUtils;

import org.springframework.beans.factory.annotation.Autowired;

import org.springframework.http.HttpHeaders;

import org.springframework.http.HttpStatus;

import org.springframework.http.MediaType;

import org.springframework.http.ResponseEntity;

import org.springframework.util.ResourceUtils;

import org.springframework.web.bind.annotation.PathVariable;

import org.springframework.web.bind.annotation.RequestBody;

import org.springframework.web.bind.annotation.RequestMapping;

import org.springframework.web.bind.annotation.RequestParam;

import org.springframework.web.bind.annotation.RestController;

import org.springframework.web.multipart.MultipartFile;import com.annotation.IgnoreAuth;

import com.baomidou.mybatisplus.mapper.EntityWrapper;

import com.entity.ConfigEntity;

import com.entity.EIException;

import com.service.ConfigService;

import com.utils.R;/*** 上传文件映射表*/

@RestController

@RequestMapping("file")

@SuppressWarnings({"unchecked","rawtypes"})

public class FileController{@Autowiredprivate ConfigService configService;/*** 上传文件*/@RequestMapping("/upload")public R upload(@RequestParam("file") MultipartFile file,String type) throws Exception {if (file.isEmpty()) {throw new EIException("上传文件不能为空");}String fileExt = file.getOriginalFilename().substring(file.getOriginalFilename().lastIndexOf(".")+1);File path = new File(ResourceUtils.getURL("classpath:static").getPath());if(!path.exists()) {path = new File("");}File upload = new File(path.getAbsolutePath(),"/upload/");if(!upload.exists()) {upload.mkdirs();}String fileName = new Date().getTime()+"."+fileExt;File dest = new File(upload.getAbsolutePath()+"/"+fileName);file.transferTo(dest);FileUtils.copyFile(dest, new File("C:\\Users\\Desktop\\jiadian\\springbootl7own\\src\\main\\resources\\static\\upload"+"/"+fileName));if(StringUtils.isNotBlank(type) && type.equals("1")) {ConfigEntity configEntity = configService.selectOne(new EntityWrapper<ConfigEntity>().eq("name", "faceFile"));if(configEntity==null) {configEntity = new ConfigEntity();configEntity.setName("faceFile");configEntity.setValue(fileName);} else {configEntity.setValue(fileName);}configService.insertOrUpdate(configEntity);}return R.ok().put("file", fileName);}/*** 下载文件*/@IgnoreAuth@RequestMapping("/download")public ResponseEntity<byte[]> download(@RequestParam String fileName) {try {File path = new File(ResourceUtils.getURL("classpath:static").getPath());if(!path.exists()) {path = new File("");}File upload = new File(path.getAbsolutePath(),"/upload/");if(!upload.exists()) {upload.mkdirs();}File file = new File(upload.getAbsolutePath()+"/"+fileName);if(file.exists()){/*if(!fileService.canRead(file, SessionManager.getSessionUser())){getResponse().sendError(403);}*/HttpHeaders headers = new HttpHeaders();headers.setContentType(MediaType.APPLICATION_OCTET_STREAM); headers.setContentDispositionFormData("attachment", fileName); return new ResponseEntity<byte[]>(FileUtils.readFileToByteArray(file),headers, HttpStatus.CREATED);}} catch (IOException e) {e.printStackTrace();}return new ResponseEntity<byte[]>(HttpStatus.INTERNAL_SERVER_ERROR);}}

4.3封装

package com.utils;import java.util.HashMap;

import java.util.Map;/*** 返回数据*/

public class R extends HashMap<String, Object> {private static final long serialVersionUID = 1L;public R() {put("code", 0);}public static R error() {return error(500, "未知异常,请联系管理员");}public static R error(String msg) {return error(500, msg);}public static R error(int code, String msg) {R r = new R();r.put("code", code);r.put("msg", msg);return r;}public static R ok(String msg) {R r = new R();r.put("msg", msg);return r;}public static R ok(Map<String, Object> map) {R r = new R();r.putAll(map);return r;}public static R ok() {return new R();}public R put(String key, Object value) {super.put(key, value);return this;}

}