四川省工程建设管理协会网站百度推广外包哪家不错

背景:我在代码里使用直连的方式在数据库中创建数据库等,由于需要适配各个数据库服务所以我分别兼容了mysql、postgresql、oracal等。但是在使用过程中会出现错误:

No suitable driver found for jdbc:postgresql

但是我再使用mysql的直连方式创建方式时没有出现问题。

代码如下:

Connection connection = null;Statement statement = null;try {connection = DriverManager.getConnection(url, loginUser, loginPwd);statement = connection.createStatement();//其他代码} catch (Exception e){LOGGER.error("创建数据库信息异常", e);result = false;} finally {close(connection, statement);}出现这个的一个原因是没有 postgresql 依赖。所以我先将依赖加入:

<dependency><groupId>org.postgresql</groupId><artifactId>postgresql</artifactId> </dependency>

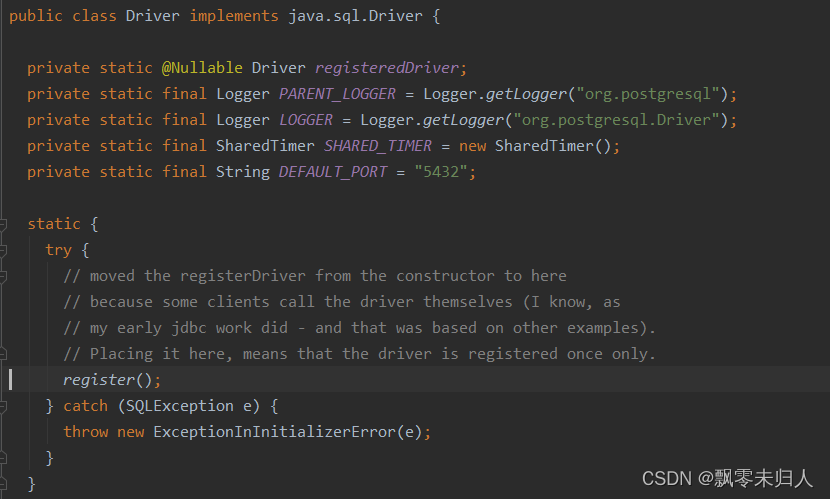

但是在之后的运行中还是提示这个错误。经过排查发现DriverManager中的driver列表只有mysql的Driver。没有postgresql的Driver。但是这个Driver的注册都是在类初始化的时候自动注册的:

所以不知道为什么他没有注册到DriverManager里面。

解决办法是我们在任意的一个地方创建一下我们需要的Driver。例如postgresql的:

Connection connection = null;

Statement statement = null;try {Class clazz = Class.forName("org.postgresql.Driver");clazz.newInstance();connection = DriverManager.getConnection(url, loginUser, loginPwd);statement = connection.createStatement();//其他代码} catch (Exception e){LOGGER.error("创建数据库信息异常", e);result = false;} finally {close(connection, statement);}这样就会自动执行其中的静态代码块,实现注册Driver到DriverManager的目的。