wordpress新站不收录电器企业网站建站

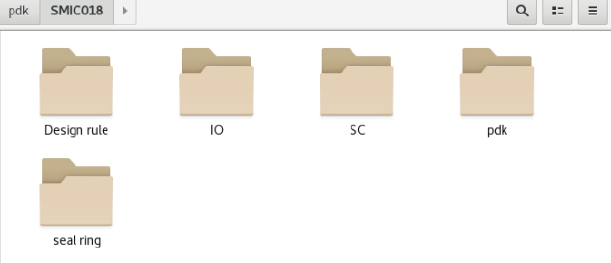

目录

PDK简介

pdk安装

Standard Cell Library简介

IO Library简介

PDK简介

PDK:全称Process Design Kit,是工艺设计工具包的缩写,是制造和设计之间的沟通桥梁,是模拟电路设计的起始点。

具体来说,PDK是代工厂(FAB)所创建的用来描述某一制程下工艺细节的文件,它主要包括:基本器件(Pcell)、模型文件(Model)、技术文件(TechnologyFile)、验证文件(Calibre/Assura)等,用来提供给设计公司进行芯片设计,设计公司通过使用PDK进行电路设计仿真,版图绘制及验证,然后将设计好的芯片交给代工厂加工生产,代工厂能够基于客户的设计生产芯片,保证芯片的预期功能和性能。

以SMIC 0.18um MS and BCD 1.8V/5V/10V/12V/20V/35V/40V PDK工具包为例介绍PDK中的内容以及安装使用。

SPDK018MS_and_BCD_1850100120200350400_OA_CDS_V1.14_REV0_0_CCIQRC.tar介绍

名称含义:

| SPDK018 | SMIC开发基于0.18um制程的PDK |

| MS_and_BCD | 该PDK是用于混合信号(Mixed-Signal)和BCD(bipolar、cmos、dmos)电路设计的工艺 |

| 1850100120200350000 | 该PDK中晶体管支持电压,有1.8v、5v、10v、12v、20v、35v、40v的晶体管 |

| OA_CDS | 该PDK支持Cadence的OA平台,即IC61以上版本 |

| V1.14_REV0_0 | PDK的开发版本号 |

| CCIQRC | 该PDK支持CALIBRE+QRC提取寄生参数 |

pdk安装

1、解压缩SPDK018MS_and_BCD_1850100120200350400_OA_CDS_V1.14_REV0_0_CCIQRC.tar.gz

tar -xzvf SPDK018MS_and_BCD_1850100120200350400_OA_CDS_V1.14_REV0_0_CCIQRC.tar.gz

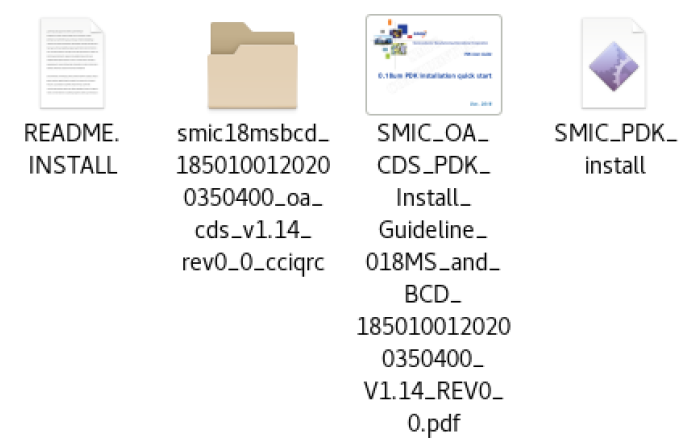

2、解压后得到如下四个文件:

README.INSTALL -->PDK安装介绍

smic18msbcd_1850100120200350400_oa_cds_v1.14_rev0_0_cciqrc -->PDK原始文件

SMIC_OA_CDS_PDK_Install_Guideline_018MS_and_BCD_1850100120200350400_V1.14_REV0_0.pdf -->PDK安装介绍pdf档

SMIC_PDK_install -->PDK安装脚本

打开smic18msbcd_1850100120200350400_oa_cds_v1.14_rev0_0_cciqrc文件夹

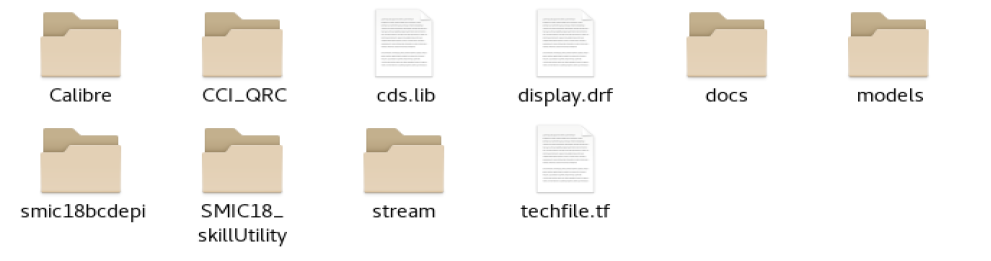

3、smic18msbcd_1850100120200350400_oa_cds_v1.14_rev0_0_cciqrc原始文件介绍

| cds.lib | Text file defining Cadence libraries |

| smic18bcdepi | Source 0.18um MS and BCD 1.8V/5V/10V/12V/20V/35V/40V PDK Cadence library |

| Calibre | Calibre DRC / LVS deck after PDK installation |

| CCI_QRC | CCI QRC deck after PDK installation |

| CCI_QRC_ALL | Original Cadence QRC package |

| DRC_ORI | Original Calibre DRC deck |

| LVS_ORI | Original Calibre LVS deck |

| SMIC18_skillUtility | Utility for batch-setting parameter values / LDMOS S/B Connection |

| models | include hspice model and spectre model |

| stream | layer mapping |

| docs | user guideline, reference manual and release note |

| display.drf | display file |

| techfile.tf | Technology file |

| assura_tech.lib | Original Assura tech file |

1、PDK安装,执行./SMIC_PDK_install

./SMIC_PDK_install

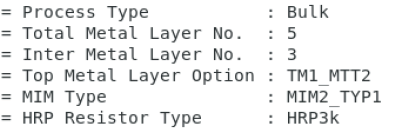

2、PDK安装,process选择及确认

3、PDK安装后文件

4、PDK安装后文件介绍:smic18_Bulk_1P5M_TM1_MTT2_HRP3k_MIM2_TYP1_oa_cds_v1.14_rev0_0_cciqrc

| cds.lib | Text file defining Cadence libraries |

| smic18bcdepi | 0.18um MS and BCD 1.8V/5V/10V/12V/20V/35V/40V PDK Cadence library |

| Calibre | Calibre DRC/LVS deck |

| CCI_QRC | CCI QRC deck |

| SMIC18_skillUtility | Utility for batch-setting parameter values / LDMOS S/B Connection |

| models | include hspice model and spectre model |

| stream | layer mapping |

| docs | user guideline, reference manual and release note |

| display.drf | display file |

| techfile.tf | Technology file |

Standard Cell Library简介

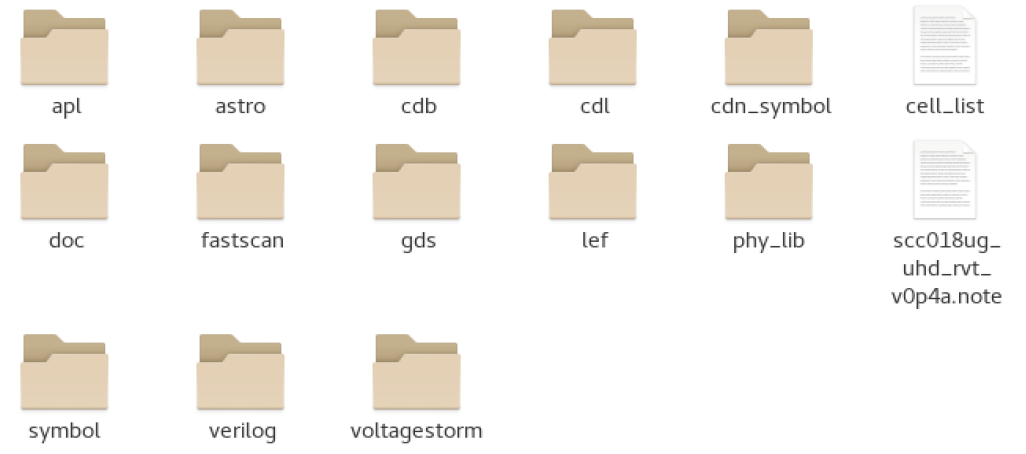

SCC018UG_UHD_RVT_V0p4a文件

| apl/ | apache power library |

| astro/ | Astro views,including the antenna information in CLF format,wire track definition,mapping file. |

| cdb/ | Celtic noise database |

| cdl/ | LVS netlist |

| cdn_symbol/ | adence Symbol for composer |

| celL_list | Cell list of this library |

| doc/ | Datasheet |

| fastscan/ | ATPG pattern for fastscan |

| gds/ | GDS database |

| lef/ | Tech file of lef & Cadence P&R library (two files included,with and without antenna information respectively) |

| phy_lib/ | Physical library |

| scc018ug_uhd_rvt_v0p4a.note | Release notes |

| symbol/ | synopsys Symbol for design vision |

| verilog/ | Verilog model for positive/negative timing check and function verification |

| voltagestorm/ | IR drop analysis |

IO Library简介

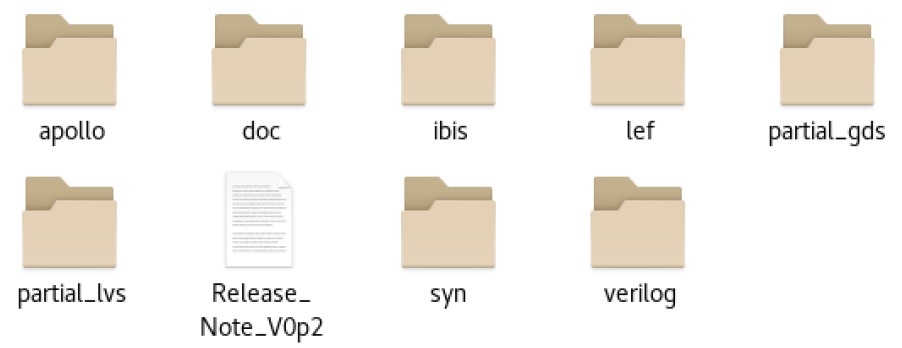

SP018MSD5SVP_V0p2文件

| apollo/ | design data for Apollo P&R flow |

| doc/ | Datasheet |

| ibis/ | IBIS (Input Output Bu er Information Specification) modelCadence P&R library |

| lef/ | Cadence P&R library |

| partial_gds/ | gds data containing all lO cells |

| partial_lvs/ | Netlist without internal circuit description and only pin for lvs |

| Release_Note_V0p2 | Release notes |

| syn/ | snopsys synthesis library |

| verilog/ | zero delay model without timing information |