整合营销推广威海百度seo

目录

- 1 下载远程工具

- 2 查看服务器配置

- 3 下载部署包

- 4 安装部署包

- 5 系统登录

- 总结

最近微搭推出了私有化部署版本,正好官方赠送了我一台云服务器,练习一下部署的过程,本篇作为一个实践的记录

1 下载远程工具

一般我们使用的是云服务器,我这里的操作系统是初始化的centos。linux服务器不像windows提供可视化的界面,我们需要下载一个远程工具来连接

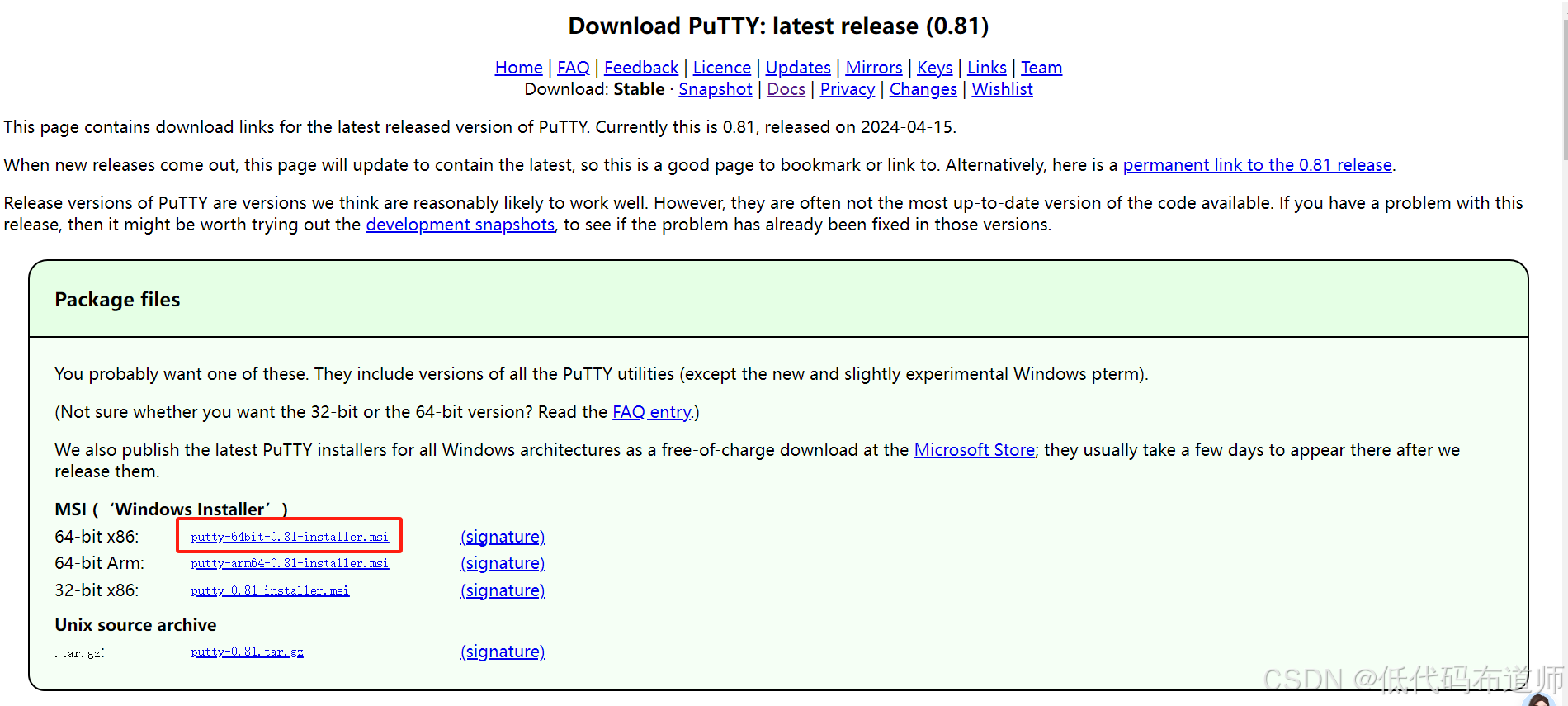

这里下载一个免费的工具,PuTTY,以下是下载链接

https://www.chiark.greenend.org.uk/~sgtatham/putty/latest.html

因为我的电脑是intel的CPU,我选择x86这个安装包

下载后在浏览器的下载目录双击安装文件

点击next安装

安装到默认C盘可以,也可以更改为自己的目录,一路下一步就完成了安装

安装好了之后,点击电脑左下角的开始菜单,找到我们的PuTT启动文件

如果需要向服务器上传文件可以点击PSFTP,我们都是网络安装不需要使用这个

打开之后填入你的服务器的公网IP

输入用户名和密码即可登录

2 查看服务器配置

登录之后我们可以查看一下服务器的配置信息,首先输入如下命令查看操作系统版本

cat /etc/os-release

我这里的版本是CentOS Linux 7

查看CPU信息

lscpu

查看内存信息

free -h

查看磁盘信息

df -h

查看网络信息

ifconfig

# 或者

ip addr

3 下载部署包

在第二步主要是要核对一下服务器的配置信息满足微搭私有化部署的最低要求,核查完就可以下载部署包,执行如下命令

wget -L -O weda.zip https://software-1302110647.cos.ap-guangzhou.myqcloud.com/beta/x86_64/weda-v0.2-beta-linux-x86_64.zip && unzip weda.zip && cd weda && chmod +x ./install.sh && chmod +x ./check-docker.sh

4 安装部署包

1、安装docker

运行如下命令安装docker

sudo ./docker-install.sh

2、安装license

打开我们控制台的私有化部署目录

复制我们的license

命令的格式是

echo 'xxxxxxx' > LICENSE.txt

这里的xxxxx需要替换成你自己的,然后把替换好的命令贴入命令行

3、让license生效

执行如下命令

sudo ./install.sh

按回车确认,之后查看我们的env文件是否正确生成

ls -lsa

如果看到.env就表示序列号配置成功了

但是提示了docker-compose: command not found 导致后续的安装失败了

先看一下我们的路径

echo $PATH

用vim命令打开install.sh文件

vim install.sh

然后把compose的路径修改一下,修改成我们本机的路径

/usr/local/bin/docker-compose --profile all up -d

再次运行命令就开始安装部署包了

5 系统登录

安装成功之后,在浏览器里输入后台地址

http://{{ip}}:80/cloud-admin/index.html

这里的{{ip}}替换成你自己的IP就行

至于应用的创建这些,和公有云操作模式是一样的,可以参考我历史的教程就行

总结

我们本篇介绍了使用远程工具登录云服务器,使用命令查看服务器配置信息,以及搭建微搭私有化部署包,感兴趣的操作一下吧。