西宁网站制作公司南通e站网站建设

【可能出现的情况】

1、未安装 Flask-SQLAlchemy:

在使用 flask_sqlalchemy 之前,你需要确保已经通过 pip 安装了 Flask-SQLAlchemy。可以通过以下命令安装它:

pip install Flask-SQLAlchemy

2、包名大小写问题:

Python 是区分大小写的,确保在导入和使用模块时大小写与实际安装的库名称一致。确保你在代码中使用的是 SQLAlchemy,而不是 SQLAlchem。

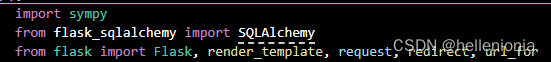

正确的导入应该是:

from flask_sqlalchemy import SQLAlchemy

3、Flask 应用程序对象创建之前导入:

确保你在创建 Flask 应用程序对象 app 之前导入 SQLAlchemy。一般来说,导入应该在创建 Flask 应用程序对象的代码之前完成。

正确的顺序应该是:

from flask import Flask

from flask_sqlalchemy import SQLAlchemyapp = Flask(__name__)

db = SQLAlchemy(app)

【执行操作】

【结果】

解除报错