网站添加新闻建站报价表

前言

在Ubuntu中操作系统中,通过Anconda安装对应的虚拟环境以及软件包,一般都需要适配Cuda、Pytorch版本等

以下安装配置都是在Ubuntu操作系统下

1. 安装Cuda

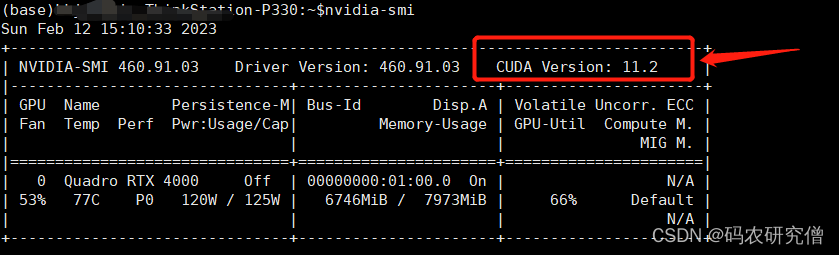

通过Ubuntu操作系统查看cuda适配的版本:nvidia-smi

截图如下:

查看Ubuntu版本可如下方式

- (1)

cat /proc/version - (2)

uname -a - (3)

lsb_release -a

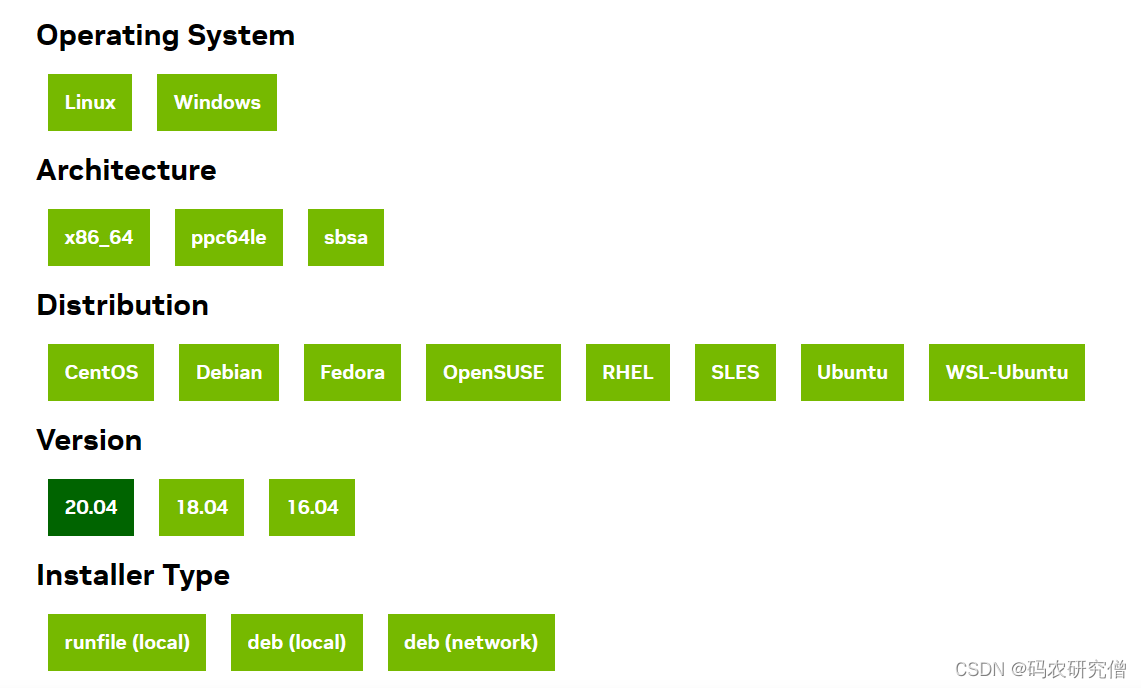

在官方选择适配的版本:Cuda官网,并选择相应的配置下载:

检查是否安装成功:nvcc -V

2. 安装Pytorch

项目文件中不需要pytorch的规定版本,可以在官方网站中选择最新即可:Pytorch最新版本