都匀网站wordpress 按钮支付

项目场景:

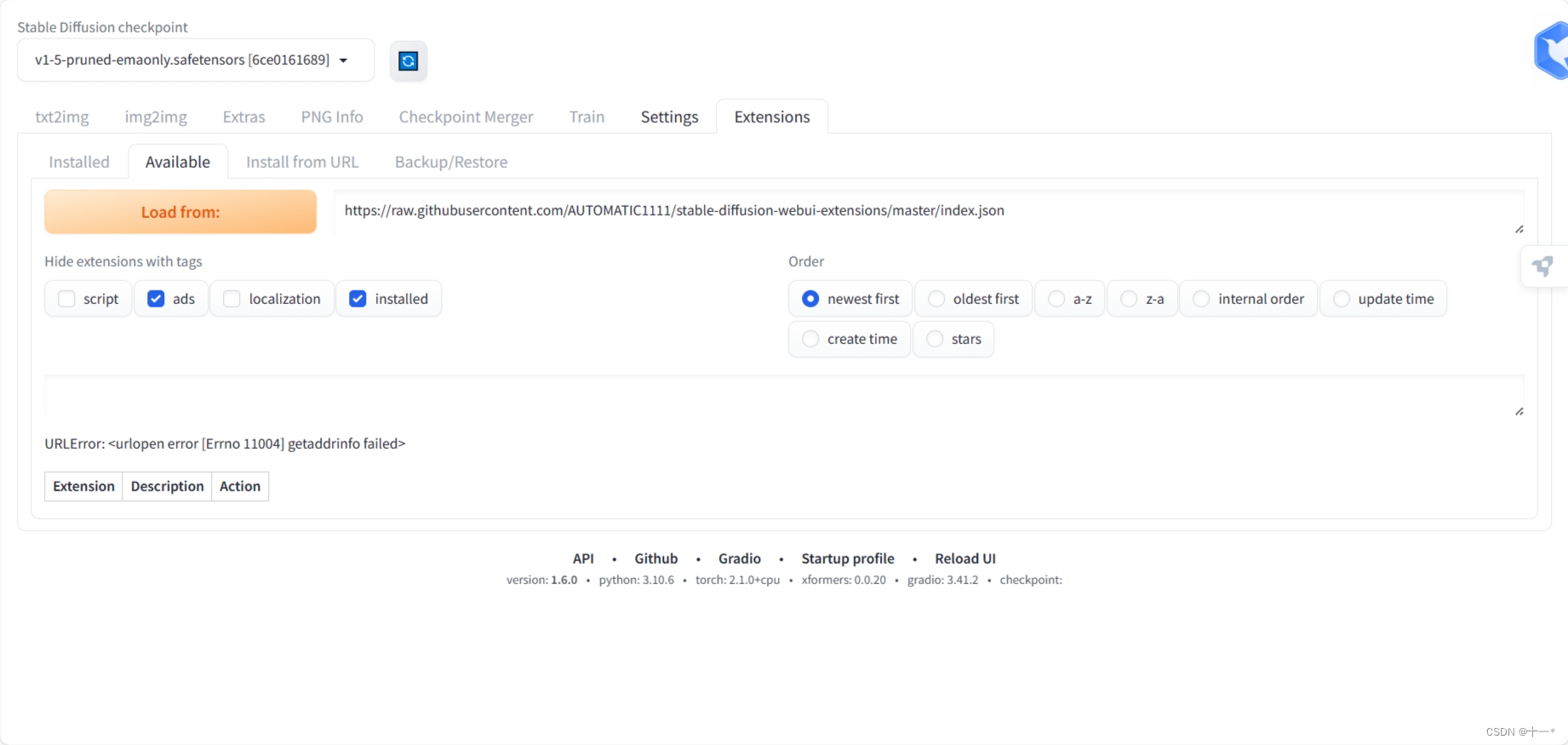

在使用Stable diffusion webui时,使用扩展列表出现错误

问题描述

点击loadfrom后,出现加载扩展列表报错

原因分析:

下载的扩展的时候,都是github 的url,需要科学上网,如果不能科学上网那就需要更改相关地址。

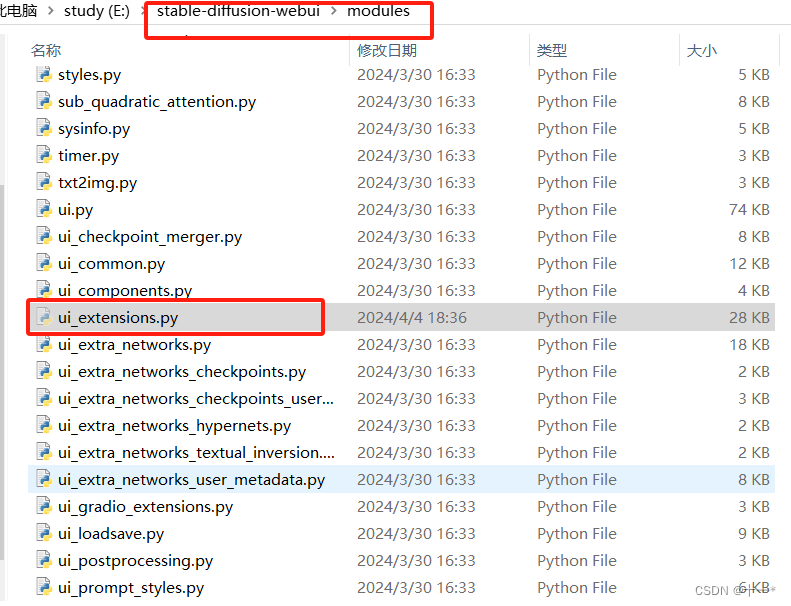

解决方案:

打开ui_extensions.py文件

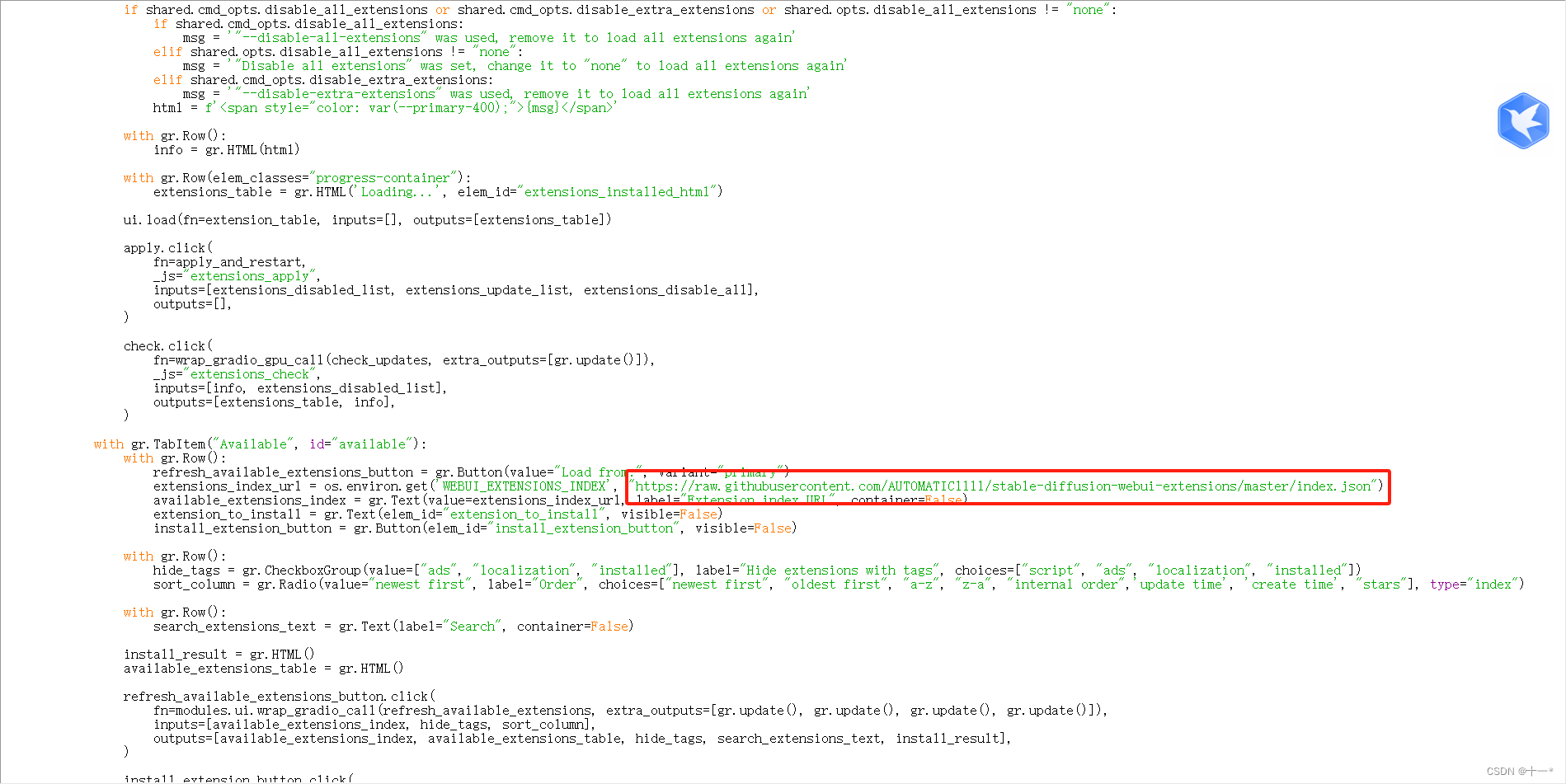

将下图红框中的地址进行替换

可替换成如下两个链接中的任何一个

1. https://gitgud.io/AUTOMATIC1111/stable-diffusion-webui/-/wikis/Extensions-index.md2. https://mirror.ghproxy.com/https://raw.githubusercontent.com/AUTOMATIC1111/stable-diffusion-webui-extensions/master/index.json

替换后重新运行webui-user.bat