模板网站平台p2p网站制作 杭州

Unity开发某个项目,打包后的apk包体已经高达1.25G了,这是非常离谱的。为了不影响用户体验,需要将apk包体缩小。因为项目本身不包含很多模型以及其他大型资源,排除法将AB包删除,发现app本身就100多M。

由此可以锁定是AB包的问题,上网上使用了UWA(Unity性能分析工具)去分析了下AssetsBundle包的冗余。

什么是UWA

UWA地址

UWA | 致力于游戏VR和AR应用提供项目研发解决方案 | 简单优化、优化简单 | 侑虎科技

UWA是一个专门为Unity游戏开发提供的性能分析和优化工具平台。它能够实时监控游戏性能数据,包括内存使用、CPU占用、帧率和DrawCall等关键指标,同时可以自动扫描项目中的性能隐患,提供具体的优化方案和建议。这个工具易于集成到Unity项目中,支持多平台开发,并提供可视化的数据分析界面,是Unity开发者进行性能优化的实用工具。

发现基本上每个Panel都会引用4-5种字体冗余。这显然是问题所在。

AssetBundle资源冗余的原因

- 依赖引用

-

- 不同的AB包引用了相同的资源

- 比如AB包A和AB包B都需要使用同一个字体

- 在打包时这个字体会被重复打包到两个AB中

- 重复打包情况

-

- 直接依赖:资源被直接放入多个AB包中

- 间接依赖:资源作为其他资源的依赖项被重复打包

- 共享资源未单独打包:多个AB包共同依赖的资源未抽取出来

解决方案

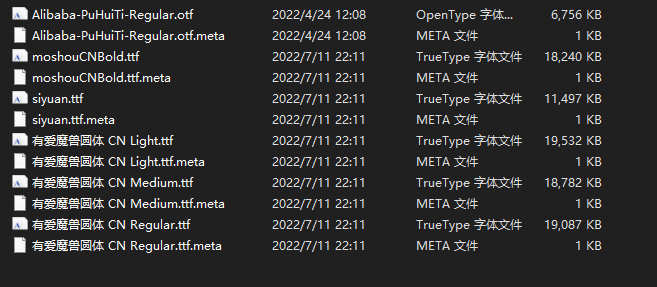

我去看了下目前项目里引用的字体大小。每个字体文件过大,有的TTF或OTF都快20MB了。

使用字体裁切技术来优化字体文件大小。通过提取项目中实际使用的文字(如"登录"、"商城"等),剔除未使用的字符,显著减小原TTF字体文件的体积。

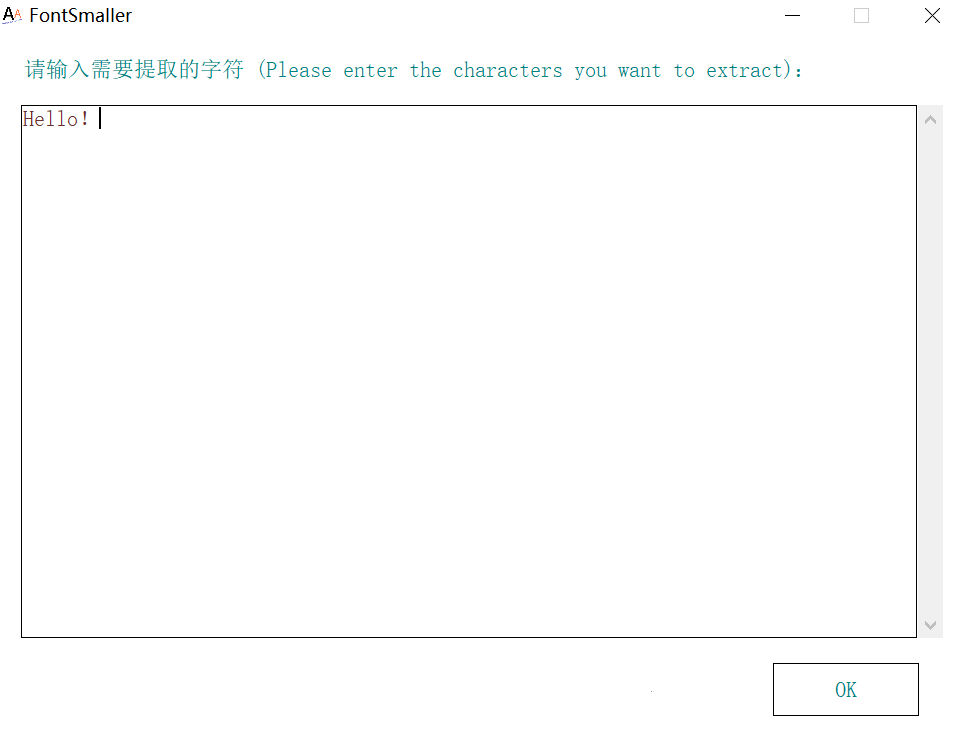

使用fontsmaller进行裁切。

FontSmaller 字体文件子集化工具

FontSmaller 字体文件子集化工具是一个免费的程序,它可以帮助用户从一个字体文件中抽出部分字符,再组成精减的字体文件,主要用于网页设计等。

主要优势:更易操作,无需安装。相较于其他在线版工具,其不受子集字符数量限制。

简单点的做法就是下载一个常用字库,比如常用3000字库,然后导入进去进行裁切。

优化后的字体文件,非常清爽了。

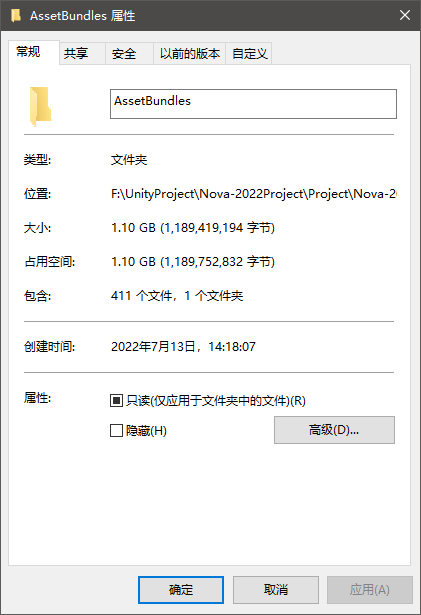

再次打AB包,发现AB包缩小到200M左右。非常Nice!

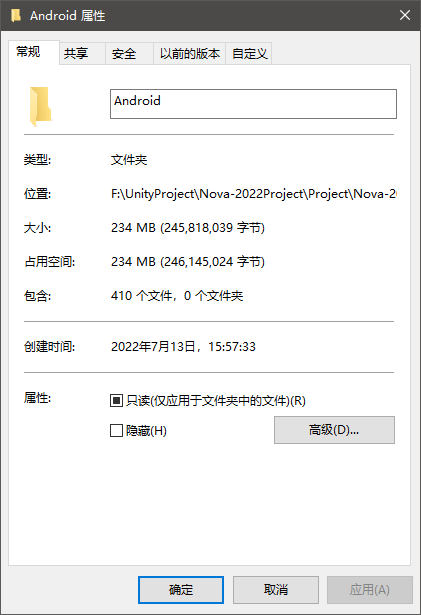

原来的大小

精简后的大小