网站制作信息浙江注册公司网站

自学第一步

第一个简单的基础,向世界说你好

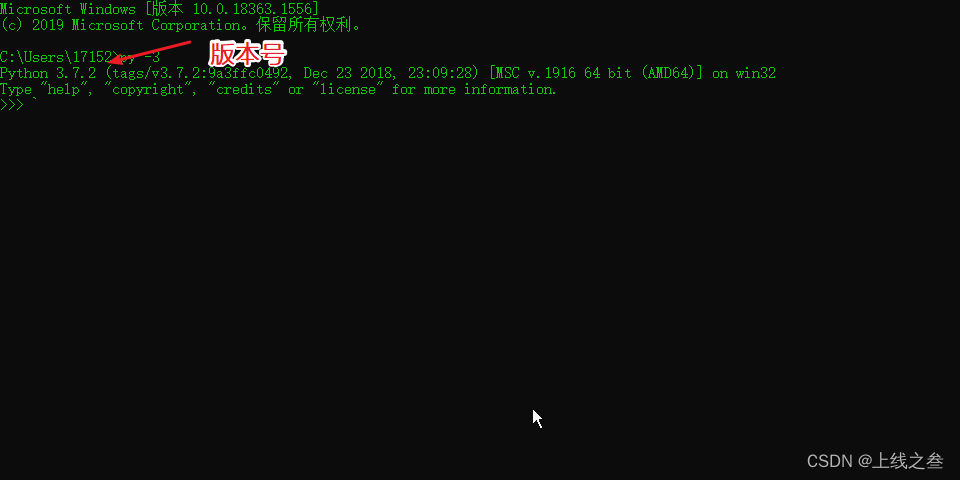

启动python

开始

print是打印输出的意思,就是输出引号内的内容。

标点符号必须要是英文的,因为他只认识英文的标点符号。

exit()推出python。

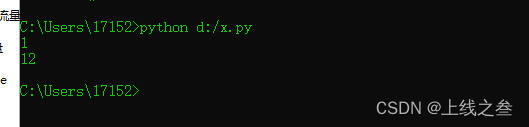

我们创建一个文本文档,把后缀改成py,我放到了d盘里面,之后右键通过笔记本模式输入print("1") print("12")

d盘是他路径的,倒他的路径哪里然后执行

也能执行出python效果。

第二章

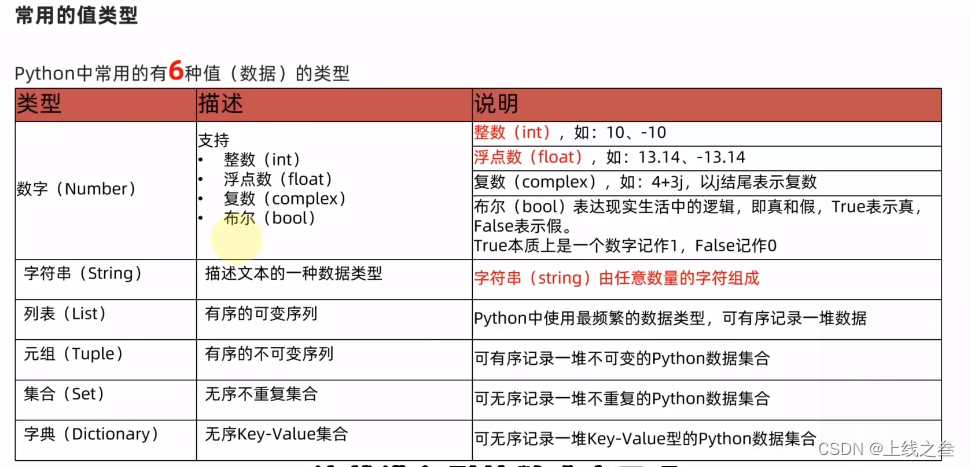

上面是字面量,在代码中写下来的固定值称之为字面量。

学习整数,浮点数,字符串。

注释的作用

注释只是一段文章说明这个程序是干嘛的,并不会影响代码的运行。方便别人看懂代码

单行注释:以#开头,和内容一般以一个空格隔开。

多行注释:一般以三个引号开头中间是内容,在以三个引号结尾。,

#变量

格式 变量名字=变量值

money = 50

在打印money的结果就变成了50