青浦做网站的公司中国空间站建造历程

目录

一、项目介绍

二、开发环境以及技术

三、概要设计

四、关键算法

五、项目演示

六、代码实现

一、项目介绍

该项目是基于负载均衡的在线oj,模拟平时刷题网站(leetcode和牛客)写的一个在线判题系统

项目主要分为五个模块:

- 编译运行模块:基于httplib库搭建的代码处理服务器,对用户提交的代码进行测试

- 业务逻辑模块:基于httplib库并结合MVC模式框架搭建oj服务器,负责题目获取,网页渲染以及负载均衡地将用户提交代码发送给代码处理服务器进行处理

- 数据管理模块:基于MySQL数据库对用户的数据、题目数据进行管理

- 会话模块:基于cookie和session针对登录用户创建唯一的会话ID,通过cookie返回给浏览器

- 公共模块:包含整个项目需要用到的第三方库以及自行编写的工具类的函数

二、开发环境以及技术

开发环境:

- 轻量应用服务器(CentOS7.6)、gcc/g++、VsCode、MySQL Workbench、Postman、Xshell 7

主要技术:

- C++ STL标准库

- C++ Boost准标准库

- cpp-httplib第三方开源网络库

- jsoncpp第三方开源序列化、反序列化库

- ctemplate第三方开源前端网页渲染库

- MVC模式框架

- 负载均衡设计

- html、css、js、jquery、ajax

- MySQL C Connect

三、概要设计

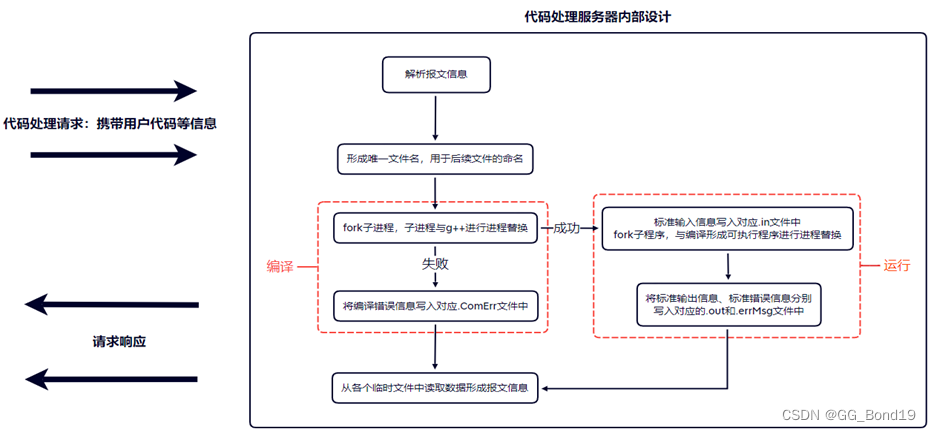

本项目将代码处理功能与主体功能进行解耦,分别实现了代码处理服务器与主服务器,从而减小各个服务器压力。服务器集群与浏览器之间属于BS架构,以剖析的角度看待,代码处理服务器集群与主服务器之间则属于CS架构(可将主服务器看作为代码处理服务器的客户端)

主服务器功能较为复杂,采用MVC模式框架,Model模型层负责与数据库层进行交互,View视图层处理对网页资源的渲染,Controler控制器负责各个模块之间统筹交互。主服务器并非反向代理服务器(还具有分发外的其他功能),但起到反向代理的功能,通过负载均衡模块与代码处理服务器集群进行网络交互

代码处理服务器相较于主服务器更加轻量,主要有编译、运行两大功能,不与浏览器进行直接交互,将编译、运行过程中产生的所有数据交付主服务器进行处理

四、关键算法

主服务器向代码处理服务器发送请求时采用最小连接数法

最小连接数算法较为灵活和智能,由于后端服务器的配置不尽相同,对于请求的处理有快有慢,该算法根据后端服务器当前的连接情况,动态地选取其中当前负载连接数最少的一台服务器来处理当前的请求,尽可能地提高后端服务的利用效率,将负责合理地分流到每一台服务器

用户登录后采用MD5算法形成SessionID,从而实现免登录功能

无论多长的字符串,计算出的MD5值都是固定长度(16字节版本或者32字节版本)。源字符串只要改变一点,最终得到的MD5值会差别很大。通过源字符串生成MD5很容易,但是通过MD5还原成原串理论上是不可能的,使得私密性更强

五、项目演示

普通用户登录界面

登录成功后,获得主界面

服务器返回的Session Id保存在浏览器的Cookie文件中

题目列表

单个题目

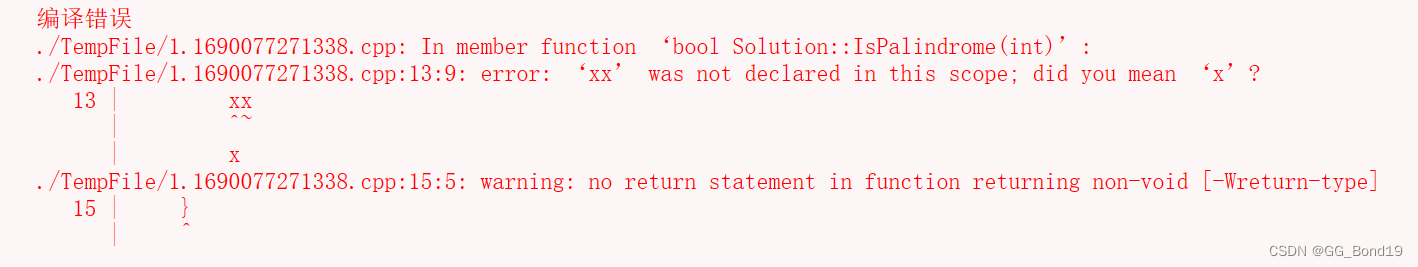

提交代码会发生的情况

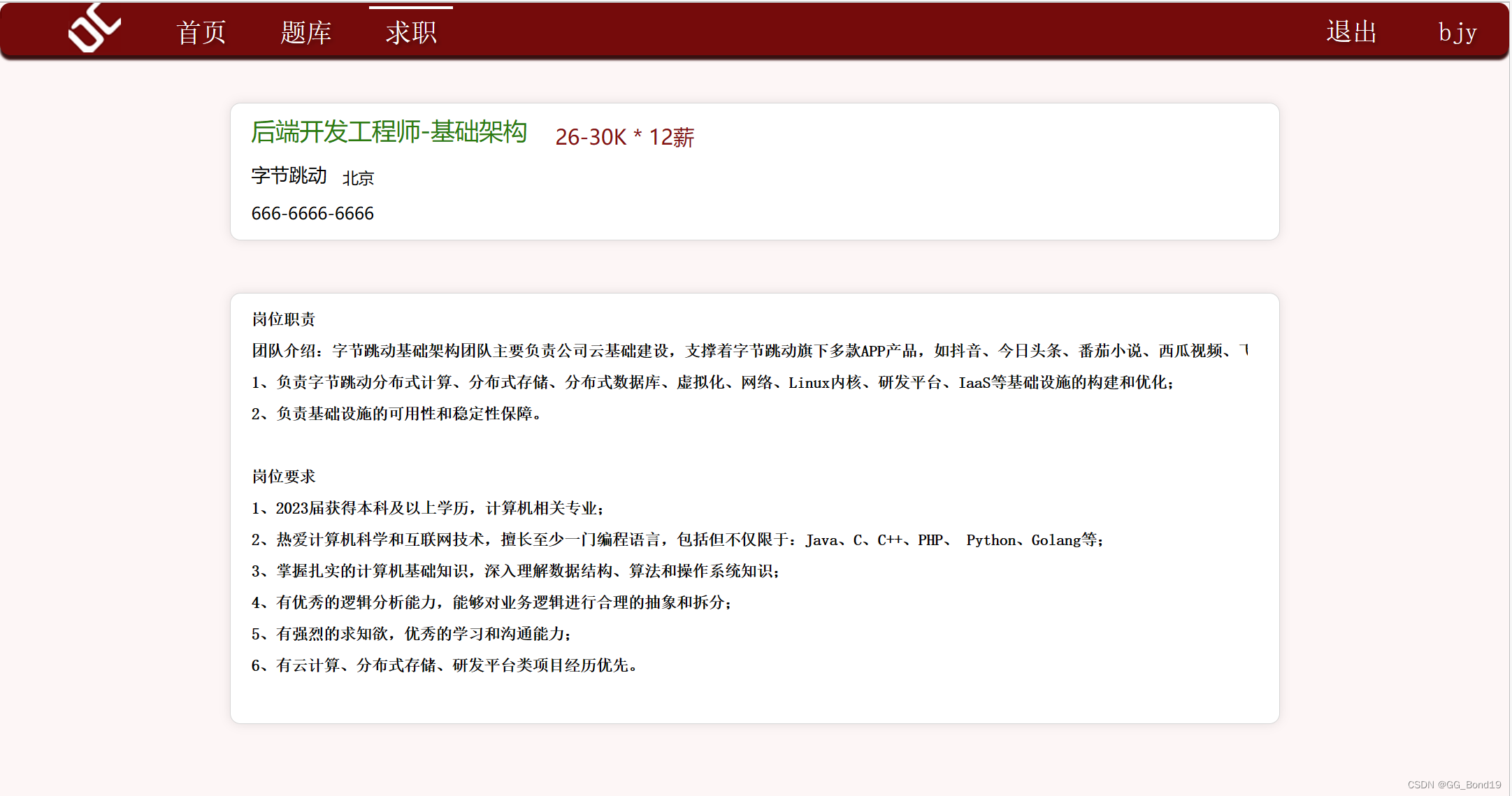

求职列表

单个职位

管理员账号登录界面

登录成功后进入管理员界面

进入录题模块,进行题目录入

进入岗位模块,进行岗位录入

六、代码实现

GG-Bruse/Load_balancing_OJ: This is a load balanced online programming evaluation platform project written in C++ language (github.com)![]() https://github.com/GG-Bruse/Load_balancing_OJ

https://github.com/GG-Bruse/Load_balancing_OJ