幼儿教育网站源码中英文网站建设费用

摘 要

网络相册设计与实现的目的是让使用者可以更方便的将人、设备和场景更立体的连接在一起。能让用户以更科幻的方式使用产品,体验高科技时代带给人们的方便,同时也能让用户体会到与以往常规产品不同的体验风格。

与安卓,iOS相比较起来,网络相册设计与实现在流畅性,续航能力,等方方面面都有着很大的优势。这就意味着网络相册设计与实现的设计可以比其他系统更为出色的能力,可以更高效的完成最新的相册分享、公告信息等功能。

此系统设计主要采用的是JAVA语言来进行开发,采用Spring Boot框架技术,框架分为三层,分别是控制层Controller,业务处理层Service,持久层dao,能够采用多层次管理开发,对于各个模块设计制作有一定的安全性;数据库方面主要采用的是MySQL来进行开发,其特点是稳定性好,数据库存储容量大,处理能力快等优势;服务器采用的是Tomcat服务,能够提供稳固的运行平台,确保系统稳定运行。通过网络相册设计与实现来提升本课题的各项功能的工作效率,提供了一个多样功能,具有良好实用性的网络相册设计与实现。

关键词:网络相册设计与实现;Spring Boot框架;JAVA语言

Abstract

The purpose of designing and implementing online photo albums is to make it easier for users to connect people, devices, and scenes in a more three-dimensional manner. It can enable users to use products in a more sci-fi way, experience the convenience brought by the high-tech era, and also allow users to experience a different experience style from traditional products.

Compared to Android and iOS, network album design and implementation have significant advantages in terms of smoothness, battery life, and other aspects. This means that the design and implementation of online photo albums can have better capabilities than other systems, and can more efficiently complete the latest album sharing, announcement information, and other functions.

This system design mainly adopts JAVA language for development, using Spring Boot framework technology. The framework is divided into three layers: control layer Controller, business processing layer Service, and persistence layer Dao. It can adopt multi-level management and development, and has certain security for the design and production of each module; In terms of database development, MySQL is mainly used, which is characterized by good stability, large database storage capacity, and fast processing power; The server uses Tomcat services, which can provide a stable operating platform and ensure the stable operation of the system. By designing and implementing a network album, the work efficiency of various functions in this project is improved, providing a diverse and practical network album design and implementation.

Keywords: Network album design and implementation; Spring Boot framework; JAVA language

目 录

摘 要 I

Abstract II

1 绪 论 1

1.1研究意义 1

1.2系统设计目的 2

1.3系统设计思想 2

2系统需求分析 3

2.1系统性能需求 3

2.2系统用例图 4

2.3可行性分析 4

2.3.1经济可行性 4

2.3.2技术可行性 5

2.3.3社会可行性 6

2.4系统开发技术 6

2.4.1 springboot框架 7

2.4.2 B/S架构 8

2.4.3 MySQL介绍 8

2.4.4 Java介绍 9

2.5系统流程分析 10

3系统设计 11

3.1系统功能结构 12

3.1.1系统结构图 13

3.2数据库设计 15

3.2.1 数据库概念设计 16

3.2.2数据逻辑结构 18

4系统详细设计 21

4.1登录模块设计 22

4.2前台系统功能模块 23

4.3后台管理员功能模块 24

4.4后台用户功能模块 25

5 软件测试 28

5.1软件测试原则 29

5.2测试用例 30

结 论 30

参考文献 31

致 谢 32

1 绪 论

近些年来,随着电子科学技术的高速发展,计算机相关行业的发展创新。衍生出了各种各样方便快捷的电子设备。如手机,电脑等。这些电子设备功能强大,方便所有类型的人们使用[1]。但这些年来,人们对手机,电脑等电子高科技产物的依赖和需求也越来越大。现在的人们已经不再满足于它们各式各样的基础功能,例如与他人通讯,上网了解信息等。人们现在更希望的是随着科技的发展,手机、电脑等高科技产品可以给自己带来更多方便快捷、简单实用的功能。同时也希望自己在使用的时候可以更轻松的掌握使用这些设备的技巧。同时,伴随着这些电子设备的出现,操作系统就显的尤为重要,电子设备各式各样功能的顺利运行都要依靠它的稳定运行。操作系统可以管理、控制计算机的硬件资源和软件资源,也是计算机最为基本的系统软件。人们所有能涉及到和使用到的软件运行几乎都离不开它。它就像人类的大脑一样,控制着计算机的各种设备[2]。但同样,操作系统在发展时自身也会出现很多问题,同样的系统不能应用在所有的硬件设备上。这个问题对于大部分的电子科技受益者来说很陌生,处理起来很有困难。会让使用者不能在第一时间使用,因此会造成很多负面的影响。

什么是网络相册设计与实现?网络相册设计与实现区别于人们司空见惯的安卓系统和iOS系统,网络相册设计与实现希望只用一整套系统就解决使用的硬件设备需要有不同的系统的繁琐问题。它的出现不仅让使用者在使用时更加方便,还可以让使用者在使用选项上有了更多选择的余地。网络相册设计与实现十分流畅,可以让使用者在使用时几乎没有任何的延迟和卡顿,可以给使用者带来十分轻松的体验[3]。并且可以在几乎我们能看到的所有电子设备上使用,大幅度的增加了网络相册设计与实现的使用范围。同时,网络相册设计与实现可以同步全部的连接对象,对于使用者来说这样的系统更加方便。它可以很精准的将使用者所需的各方面的相册分享需求通过该系统提供给使用者,并且它的使用普遍性可以让各个年龄段的使用者都能有一个良好的使用体验。

1.1研究意义

伴随着科技的进步,时代的发展,越来越多的电子设备也随之出现在人们的眼前,在电子设备,软件技术成熟之前,人们可以选择使用电子设备,通过软件的帮助,找到最适合自己,最符合自己的管理方式。而网络相册设计与实现的普及也伴随着很多问题,有的软件不能适应用户使用的电子设备的系统,这会让部分使用者对这款软件彻底否认,会导致该系统失去预想的市场竞争力,面临淘汰。使用者更希望自己使用的网络相册设计与实现可以在完成最基本的功能需求的基础上变的更加稳定,流畅,并且没有任何因兼容性而引发的复杂问题[4]。

而网络相册设计与实现的出现也渐渐让这种类似的问题有了一个相对明确的解决方案,网络相册设计与实现可以使软件的运行速度变的更快,并且可以同步全部的连接对象,可以确保项目的正确运行,同时,在如此信息化的时代里,使用者对软件的各项要求也越来越多,在如此广阔的信息量之下,使用者更希望自己使用的系统可以畅通无阻的浏览每个网页上的信息,可以全方位的查询相册分享、公告信息等的特点,根据自己的需求,选择最适合自己的方案[5]。并且让整个电子信息时代都注入了新鲜的血液,且能更好的流向各个领域,各个行业,为电子信息时代继续发光发热。

1.2系统设计目的

为了适应电子信息时代和科技化时代的到来,并且应对今后可能越来越广泛的信息化的发展,需要做出了更加超前时代的功能应对。在这个高速发展的时代里,使用者对信息管理系统的要求也是越来越高,使用者都希望自己可以有拥有一款符合当今科技发展时代,且具有科技感,功能齐全的系统。希望可以只通过一个系统就可以轻松完成自己的需求,而不再因为信息的复杂而不知如何做出最佳选择。科技时代带给了人们轻松,立体的体验,而网络相册设计与实现就符合大家对科技时代的系统所拥有的期待,它可以提升用户的使用体验[6]。

1.3系统设计思想

想要做一个完整的系统,就必须要为其制定一套详细并且规范的原则。这些原则定可以帮助我们在设计过程中能有一个更好的设计理念和设计方向,可以让系统变的更加立体,更加完美。变成更加符合使用者所希望的模样。所以为了能够更好的完成系统,对系统制定了一些原则:

(1)以人为本原则

这个网络相册设计与实现,它的本质是为人们服务。是希望其可以实现并满足广大使用者对科技时代下的网络相册设计与实现的憧憬与向往。如何解放需要人工才能完成的部分和提升使用者的使用观感是最为基础的也是最重要的。它的设计宗旨就是为使用者服务。明确使用者的想法和需求,设法让使用者可以真实的感受到科技时代的魅力是设计的初衷。网络相册设计与实现可以满足新时代使用者的需求,让使用者能够真实的感受到它的便捷[7]。

(2)可修改原则

设计系统时并不能确保让所有的功能都达到使用者最理想的要求,在设计的过程中可能会有纰漏。所以在设计时要确保可以及时对不完整,不完美的部分进行修改和补充。同时,也要确保在系统发行后,在出现bug时可以在不影响使用者使用的情况下对系统进行线上维护[8]。同时要确保在修复,更新,维护的同时可以保证使用者的体验。

2系统需求分析

需求分析的首要是要分析用户的需求,知道用户存在的一些情况,并且要明确用户的使用状况,然后设计规划解决的问题。其中在使用定性的分析以及定量的分析,从这两个方面获取用户的需求。一方面定性的分析获得的应该是用户的基本需求,能够发现现在人们的习惯要求。所以定性的需要主要是为了多与用户交流,从而更为深刻的了解一些存在的需求问题;定量的分析则是发现一些潜在的用户,并且获得不一样的反馈内容[9]。所以定量的需求要让用户来阐述一些情况,一定让使用者清晰的进行客观的描述,这样才能够比较全面的获得用户的需求所在。

2.1系统性能需求

(1)鉴于该系统是一款面向全体使用者的系统,管理者需要录入使用者的个人信息、给予使用者应有的权限,让使用者可以更加自由的使用系统。

(2)要给予用户更高的查询权限,让用户可以全方位的了解本课题,让用户可以查询到相册分享、公告信息等。

(3)要提升用户的使用效率,让用户可以更加快捷的查询自己想要查询的东西。同时,还要做到同步性,在用户查询信息或者修改信息的同时,系统可以及时反馈到数据库上,进行及时更新和修复[10]。

2.2系统用例图

本系统采用自上往下的方法开发,基本定位如下功能:

本课题要求实现一套网络相册设计与实现,系统主要包括管理员模块和用户模块的功能模块;

(1)管理员用例图如下所示:

图2-1管理员用例图

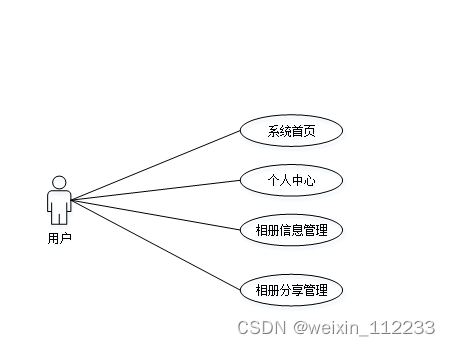

(2)用户用例图如下所示:

图2-2用户用例图

2.3可行性分析

2.3.1经济可行性

任何系统在开发之前,经济方面的问题都是最应该被考虑的,经济问题主要体现在两个方面。一方面是在开发时,现有可使用的设计资源能否满足系统的预计开发消耗;另一方面是在开发以后,系统的盈利能否保证系统的正常运行和日复一日的更新消耗。

开发方面,因为在开发系统时使用的开发工具基本都是免费的,只有一些少量的人工费。所以,开发工具上的经济消耗都是很少的,都是在可控范围内的。另外,可以在确保质量的前提下,尽可能的减少设计成本,可以为开发之后的工作留下更多的经济资源。

在最大限度降低开发成本的同时,也可以让使用者最大限度的从系统中获利,对双方来说都是一个可行的网络相册设计与实现。总结下来就是,该系统的各项开发费用都处于可控范围内[11]。经过了种种分析和考虑后证明,该系统软件可以行得通的,经济方面的压力是在预料之内的。

2.3.2技术可行性

在研究技术可行性的时候,系统的开发环境是可以确定的,所以技术可行性最好与系统功能和性能以及一些实际的情况同时考虑。在可行性研究阶段,结合实际调整开发的内容和选择能够完成的技术体系是一个可用的手段,如果系统进入开发阶段,任何的调整都意味着会耗费更多的经历。需要再次明确的问题是,技术可行性不只是考虑在技术上是否可实现,实际上还包含了在当前的实际的情况下的技术可行性。有很多的因素例如时间不足、预期的开发目标技术难度比较难、不能有充足的技术积累、而且对于技术的掌握不够等这些实际存在的情况,都是要提前部署和认真规划的。

开发网络相册设计与实现的技术内容分析,目前的状况是从网络硬件和相关技术上看是可行的。该系统采用了JAVA和 MySQL技术[12]。到现在可以知道,很多的基础知识都是经过学习使用的,在后续的设计中还需要不断的练习,学习更多相关的技术经验来充实自己对于系统的开发。

2.3.3社会可行性

在社会可行性分析中,首先能结合国家经济和社会发展的实际情况,还需要能够让用户更加的便利,给使用者带来多方面的高效益,使得可以比较快速的发展以及应用,随着很多领域的发展,尤其是智能化的社会下,据统计许多的人都拥有属于自己的系统,这种情况下就带来很多的问题,比较突出的就是管理上的不足,从而出现低效率的原因。

在可行性分析中的收益分析,是比较清晰地发掘开发的系统带来的各种直接的有效的利益以及一些隐藏起来的好处,以便在后续的设计中更加的坚定和确信系统开发的意义。解决一些社会方面存在的问题,设计并开发系统肯定是要发现某类社会存在的问题,并且能够带来一定的社会价值。还有一些社会的影响力,是通过系统想优势和切实的好处来产生的,能够在一定的情况下提高效率,肯定会增加一些社会的进步和发展。社会上的可行性,包括法律上的可行性,也包括法律上的可能性,法律上的可行性,需要社会上的许多因素,可以来实现系统建设的现实性。如果所开发的系统与国家法律或政策等相关的因素不相符合,在某些信息化的邻域中使用的是一些加密的信息或者技术问题,还有不经过正常的操作使用其他的一些公开的信息等这些情况,这样的系统的开发在法律的范围中就是不能被允许的。

其中还有一个比较重要的用户使用可行性也是通过执行系统时的可行性,是从所有情况下用户的角度来考虑系统的可行性,由于设计开发相关的系统就是站在社会中广大的用户体验考虑的,所以在这个层面考虑也是符合的。

2.4系统开发技术

2.4.1 springboot框架

该框架拥有自己独特的配置方式,网站开发人员不需要再进行大量重复的样板 式的配置工作,开箱即用,不会生成额外代码量,不需要进行XML文件的配置。

2.4.2 B/S架构

B/S结构就是指系统客户端与服务器分离,客户端通过浏览器访问服务端进行操作。

B/S结构目前广泛应用于绝大部分系统搭建中,这种结构摒弃C/S结构客户端服务端不分离的缺点,具有更多的优势:

(1)跨平台性:B/S的标准由标准化组织确立,适用于绝大多数的系统搭建,通用于应用之间。

(2)低维护成本:客户端和服务器端分离,减轻了两端的压力,尤其是客户端,对客户端设备,硬件、软件要求都比较低,并且系统需要升级或维护时,只需要在服务器端升级或维护就可以,使相应的费用减少。

2.4.3 MySQL介绍

MySQL 是一种关联数据库管理系统,该系统速度快而且灵活性强,主要原因是它将数据保存在不同的表中,MySQL软件的优点是成本低、体积小、速度快,开放源码,所以一般中小型网站的开发都选择 MySQL 作为网站数据库。

2.4.4 Java介绍

Java 最大的两个特点就是功能强大和简单易用。Java可以让程序员进行复杂的编程而不必为储存管理对象等问题所烦恼,把精力和时间更多的放在研发与设计上,极大地提高了开发者的工作效率和工作热情。

2.5系统流程分析

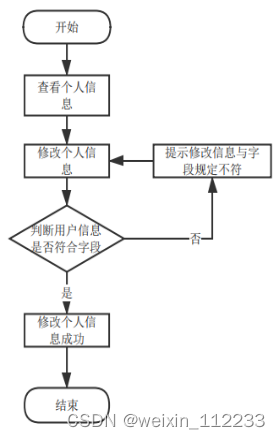

(1)个人信息流程图

用户在成功进入系统以后,可以获得用户账号、用户姓名、性别等个人信息。获得个人信息的流程见图2-3所示。

图2-3个人信息流程图

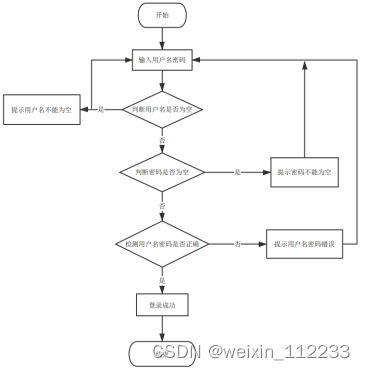

用户进行登录操作的流程图如图2-4。

图2-4 用户登录界面流程图

用户进行注册操作的流程图如图2-5。

图2-5 用户注册流程图

3系统设计

系统设计要提出具体的软件功能及要求,是系统分析后进行的流程。它的主要目的是提供软件开发的思路和具体流程,是系统运行的根本保障。它要确定软件各个模块的功能,并形成相应的流程图,方便设计者思考。同时要将每个模块需要完成的任务详细的表达出来,并对每个模块进行具体化的设计分析,提供相当数量的设计方案,再通过设计者的详细分析和比对,选择出最佳的方案进行设计开发。并对相应的方案进行验证和拓展。

3.1系统功能结构

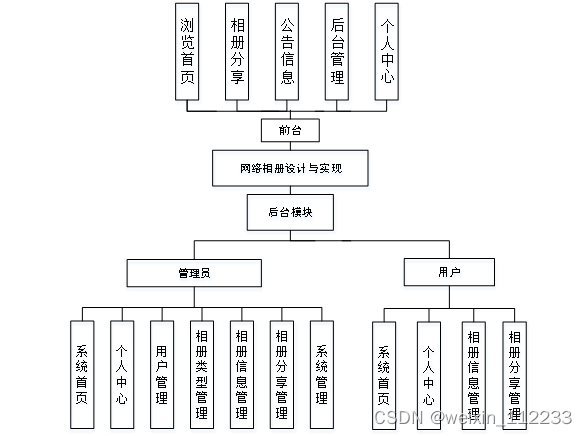

3.1.1系统结构图

系统结构图可以把杂乱无章的模块按照设计者的思维方式进行调整排序,可以让设计者在之后的添加,修改程序内容的过程中有一个很明显的思维方向。同时结构图还可以让设计者以外的其他人更直观的看出整个系统的设计理论和设计过程。让系统的设计变的更直观。该系统的功能架构图如图3-1所示:

图3-1 网络相册设计与实现功能结构图

3.2数据库设计

3.2.1 数据库概念设计

从系统运行完整的角度出发,设置相应的实体,明确各实体之间的联系。下面列举整个系统中涉及核心功能的实体:

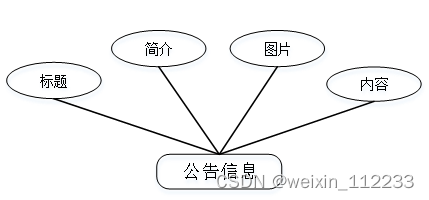

1、公告信息实体

图3-2公告信息实体图

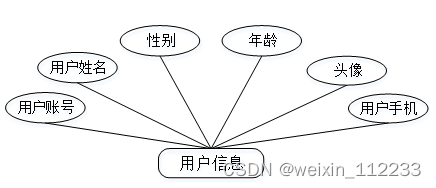

2、用户信息实体

图3-3用户信息实体图

3、相册信息实体

图3-4相册信息实体图

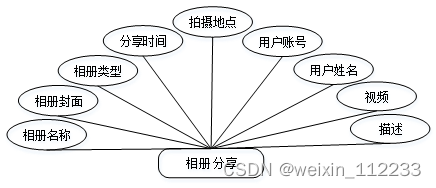

4、相册分享实体

图3-

5 相册分享实体图

3.2.2数据逻辑结构

在综合了以上对系统的设计,和对数据库的分析,同时结合了以往对数据库的使用经验后,构建了以下几张表,以下为每张表的内容:

表3-1:用户表

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

username varchar 100 用户名

password varchar 100 密码

role varchar 100 角色 管理员

addtime timestamp 新增时间 CURRENT_TIMESTAMP

表3-2:token表

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

userid bigint 用户id

username varchar 100 用户名

tablename varchar 100 表名

role varchar 100 角色

token varchar 200 密码

addtime timestamp 新增时间 CURRENT_TIMESTAMP

expiratedtime timestamp 过期时间 CURRENT_TIMESTAMP

表3-3:关于我们

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

title varchar 200 标题

subtitle varchar 200 副标题

content longtext 4294967295 内容

picture1 longtext 4294967295 图片1

picture2 longtext 4294967295 图片2

picture3 longtext 4294967295 图片3

表3-4:相册信息

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

xiangcemingcheng varchar 200 相册名称

xiangcefengmian longtext 4294967295 相册封面

xiangceneirong longtext 4294967295 相册内容

tianjiashijian date 添加时间

paishedidian varchar 200 拍摄地点

yonghuzhanghao varchar 200 用户账号

yonghuxingming varchar 200 用户姓名

shipin longtext 4294967295 视频

miaoshu varchar 200 描述

gongkaizhuangtai varchar 200 公开状态

表3-5:相册类型

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

xiangceleixing varchar 200 相册类型

表3-6:相册分享

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

xiangcemingcheng varchar 200 相册名称

xiangcefengmian longtext 4294967295 相册封面

xiangceneirong longtext 4294967295 相册内容

xiangceleixing varchar 200 相册类型

fenxiangshijian date 分享时间

paishedidian varchar 200 拍摄地点

yonghuzhanghao varchar 200 用户账号

yonghuxingming varchar 200 用户姓名

shipin longtext 4294967295 视频

miaoshu varchar 200 描述

thumbsupnum int 赞 0

crazilynum int 踩 0

clicktime datetime 最近点击时间

clicknum int 点击次数 0

表3-7:关于我们

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

title varchar 200 标题

subtitle varchar 200 副标题

content longtext 4294967295 内容

picture1 longtext 4294967295 图片1

picture2 longtext 4294967295 图片2

picture3 longtext 4294967295 图片3

表3-8:收藏表

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

userid bigint 用户id

refid bigint 商品id

tablename varchar 200 表名

name varchar 200 名称

picture longtext 4294967295 图片

type varchar 200 类型(1:收藏,21:赞,22:踩,31:竞拍参与,41:关注) 1

inteltype varchar 200 推荐类型

remark varchar 200 备注

表3-9:公告信息

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

title varchar 200 标题

introduction longtext 4294967295 简介

picture longtext 4294967295 图片

content longtext 4294967295 内容

表3-10:相册分享评论表

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

refid bigint 关联表id

userid bigint 用户id

avatarurl longtext 4294967295 头像

nickname varchar 200 用户名

content longtext 4294967295 评论内容

reply longtext 4294967295 回复内容

表3-11:配置文件

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

name varchar 100 配置参数名称

value varchar 100 配置参数值

表3-12:用户

字段名称 类型 长度 字段说明 主键 默认值

id bigint 主键

主键

addtime timestamp 创建时间 CURRENT_TIMESTAMP

yonghuzhanghao varchar 200 用户账号

mima varchar 200 密码

yonghuxingming varchar 200 用户姓名

xingbie varchar 200 性别

nianling varchar 200 年龄

touxiang longtext 4294967295 头像

yonghushouji varchar 200 用户手机

4系统详细设计

4.1登录模块设计

这个功能模块用来让工作人员进行后端登录。管理人员通过网站。在输入自己的用户名和密码、角色进行登录,登录后管理人员就可以对后台的信息相关的操作。

首先,设计后端管理的登陆页面。对页面的各个板块进行详细的设计,规划它们的字体大小,背景颜色,字体颜色和板块大小等。还要加上图片,让页面被设计的更加美观。以便让以后需要登陆的管理员可以直观的使用。

4.2 前台系统功能模块

当游客打开系统的网址后,首先看到的就是首页界面。在这里,游客能够看到网络相册设计与实现的导航条显示首页、相册分享、公告信息、后台管理等。系统首页界面如图4-1所示:

图4-1系统首页界面

在系统首页点击中间的注册/登录按钮,然后页面跳转到注册登录界面,后来输入信息完成后,单击注册或者登录操作,如图4-2所示:

图4-2用户注册、用户登录界面

用户点击相册分享;在相册分享页面的搜索栏输入相册名称,进行查询,还可以查看相册名称、相册封面、相册类型、分享时间、拍摄地点、用户账号、用户姓名、视频、描述等信息,然后也可以点击收藏等操作;如图4-3所示。

图4-3相册分享界面图

用户点击公告信息:在公告信息页面的搜索栏输入标题,进行查询,还可以查看标题、简介、发布时间、公告信息等内容,如图4-4所示。

图4-4公告信息界面图

在个人中心页面可以输入个人详细信息,进行信息更新操作,还可以对我的收藏进行详细操作,如图4-5所示:

图4-5个人中心界面

4.3后台管理员功能模块

管理员通过登录页面填写用户名和密码选择角色,完成后进行登录,如图4-6所示。

图4-6管理员登录页面

管理员登录进入网络相册设计与实现可以查看系统首页、个人中心、用户管理、相册类型管理、相册信息管理、相册分享管理、系统管理等信息,如图4-7所示。

图4-7管理员功能界面图

管理员点击用户管理;在用户管理页面对用户账号、用户姓名、性别、年龄、头像、用户手机等信息,进行查询,新增或删除用户信息等操作;如图4-8所示。

图4-8用户管理界面图

管理员点击相册类型管理;在相册类型管理页面对相册类型等信息,进行查询,新增或删除相册类型等操作;如图4-9所示。

图4-9相册类型管理界面图

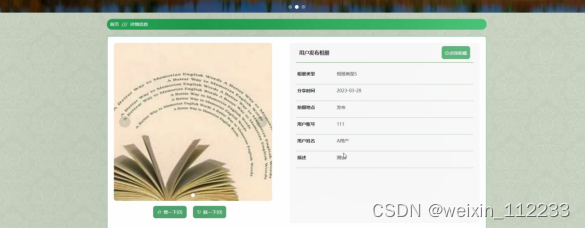

管理员点击相册信息管理;在相册信息管理页面对相册名称、相册封面、添加时间、拍摄地点、用户账号、用户姓名、视频、描述、公开状态等信息,进行查询或删除相册信息等操作;如图4-10所示。

图4-10相册信息管理界面图

管理员点击相册分享管理;在相册分享管理页面对相册名称、相册封面、相册类型、分享时间、拍摄地点、用户账号、用户姓名、视频、描述等信息,进行查询或删除相册分享等操作;如图4-11所示。

图4-11相册分享管理界面图

管理员点击系统管理;在系统管理页面对系统简介、轮播图管理、公告信息、关于我们等信息,进行查询或删除系统信息等操作;如图4-12所示。

图4-12系统管理界面图

4.4 后台用户功能模块

用户点击后台管理,然后页面跳转到用户主页面,可以对系统首页、个人中心、相册信息管理、相册分享管理等功能进行相应操作,如图4-13所示。

图4-13用户功能界图面

5 软件测试

软件测试(Software Testing)是指在设计基本完成后对软件的各项功能进行测试,检测其能否达到在系统设计之初对其的预期情况[13]。预估系统上线后的情况,对出现问题的地方进行及时修改。软件测试作为系统设计的最终阶段,它的准确性往往影响了系统的最终使用感。因为软件是由数据、文档以及程序代码组成的,所以软件测试的对象就不仅仅是程序的本身,还有包括软件设计过程中形成的数据、文档等。但软件测试也存在着问题,软件测试注重的是软件设计的最终结果,其并没有关心整个系统在开发过程中发生的问题。软件测试必须假设和考虑在设计过程中发生的问题。并对软件测试中发现的问题进行回归测试。要更好的通过软件测试检测系统以更好的找出问题来提高系统的质量。软件测试要以最少的人力和经济消耗来完成系统的设计结尾工作。而且所有的测试都要以人为本,任何的测试都要考虑到用户使用的实际体验感,要确保用户有一个好的使用体验[14]。要确保整个软件测试过程都按照原定的规则进行,以确保最终设计的系统的完整性和实用性。

5.1软件测试原则

编筐编篓,重在收口。软件测试的完成效果直接影响到整个系统的使用效果。对于软件测试来说,如果能早点发现系统的漏洞,就能及时修改,可以让设计的成本减少。进行软件测试的时候,测试员们需要制定自己的测试脚本,让这个脚本尽可能多的覆盖系统需要测试的各个路径,避免系统疏漏。同时,在软件测试的过程中,要检测程序有没有进行与系统预期功能要求无关的代码运行。避免多余的程序运行对系统产生破坏,降低效率,增加成本[15]。同时在测试后,还要尽量保留所有测试用例,这样可以帮助日后想要修改时可以及时找到原先的用例,可以再直接进行测试。以下是总结下来比较重要的一些软件测试原则:

(1)要尽可能早的进行软件测试。

随着系统的设计进行,设计过程中每一个阶段发生的错误都有可能导致在后续的开发设计的时候连续出错,如果等到软件设计工作基本全都完成再进行测试,可能会导致大量的错误同时出现,而且很难找到它们出错的源头。因为开发设计的每一步都与后续程序紧密相连,如果不及时找出错误,可能会因一处错误导致后续整个程序瘫痪。所以要坚持尽早进行软件测试的原则,一来可以减少牵一发而动全身的错误,二来可以降低成本。

(2)软件测试证明软件存在缺陷。

通过软件测试可以检测系统设计时是否存在错误和缺陷,但并不能说明系统是不存在任何缺陷的。软件测试的目的是辅助软件开发,让程序员可以尽可能早的发现错误,提高质量。软件开发的过程或多或少都会产生一些错误,软件测试就是尽可能地发现错误和缺陷,尽可能优化程序。

(3)缺陷集群效应原则。

一个软件核心的地方可能就只有那么小的一部分,但就是那一小部分,却能引发软件大规模的损坏。当我们进行软件测试的时候要特别注意那一小部分,也就是核心的部分,因为它们几乎控制了整个软件的稳定性,它们是最容易出现错误的,控制好它们几乎就控制了软件的八成稳定性。但我们也不能只仅限于这小部分模块的检查,也要对剩余的地方进行适当的测试。

(4)以人为本原则。

网络相册设计与实现设计的目的就是为人服务,任何的缺陷和错误的修改方向都要在使用者的角度去进行。要做到尽可能贴近使用者的日常模式,从使用者的角度去出发,去修改。

(5)经常更新测试方式。

测试人员应该尽量避免对系统所有的部分都使用同一种测试方式。一些测试方式只能检测特定的模块,并不能对整个系统都进行有效的测试,甚至无法发现一处错误。所以,为了能更好的发挥软件测试的作用,软件测试的时候应该经常更新测试方法,让测试的质量最大化。

5.2测试用例

部分系统测试用例如表5-1所示。

表 5-1 测试用例表

测试功能、流程 预期结果 实际结果 结论

进行登录实验。需要管理员输入相应的信息验证,看能否进入 录入信息验证通过,

转入管理员界面 登陆成功,

成功跳转页面 测试成功

对用户的登录进行测试。管理员就录入特定的信息,看能否成功登录 录入特定信息,

可以登录,可以在数据后台找到信息 可以登录,在后台找到了对应信息 测试成功

测试登录功能是否符合规定。测试员要输入错误的登录信息,检查能否登录 在输入错误的信息后,系统会发现错误,禁止测试人员登录

输入错误信息后,系统禁止登录 测试成功

对兼容性进行测试,让软件在不同的电子类产品上进行登录测试 都可以成功打开软件,正常运行 可以在不同的设备上和其他软件共存 测试成功

续表5-1

测试功能、流程 预期结果 实际结果 结论

安装测试,在试验机上登录软件,检测能否按预期正常运行 登录后可以进行正常操作,可以发行 在试验机上可以正常运行,没有卡顿 测试成功

结 论

网络相册设计与实现通过 springboot框架、JAVA语言等技术完成的。系统可以完成用户的基本需求,并且在测试中系统运行情况良好,没有出现异常。但是,还是有许多我需要学习和完善的地方。

网络相册设计与实现实现了模块化连接,对应不同的平台可以进行针对性部署,可以进行全方位的覆盖。它实现了跨终端无缝协同体验。但碍于网络相册设计与实现刚进入市场发行不久,它的各项数据,功能还没有达到完美的地步。需要进一步的实际运行来完善有缺陷的地方。在这个信息化的时代大家都希望手里的任何一个电子设备都可以完成平时的常见功能,通过网络相册设计与实现的开发可以实现这一目标。网络相册设计与实现作为国产系统,它的发展前途十分明亮,未来也会拥有很广泛的市场,通过未来的长时间发展,网络相册设计与实现的软件开发一定会成为一种趋势,让中国的操作系统发展得到进一步的提升。

参考文献

[1]张荣超.鸿蒙应用开发实战[M].人民邮电出版社.2021(1):34-70.

[2]董昱.HarmonyOS鸿蒙应用程序开发[M].清华大学出版社.2020:30-45.

[3]HarmonyOSIoT设备开发实战[M].人民邮电出版社,2019(1):40-56.

[4]鸿蒙操作系统开发入门经典[M].人民邮电出版社,2021(1)60-75.

[5]武延军.鸿蒙第三方组件库应用开发实战[M].人民邮电出版社,2021(12):40-78.

[6]华为软件技术有限公司.移动应用开发[M].清华大学出版社,2021:15-25.

[7]李亚玲, 韩奥, 鲁建丽, 张航.软件测试初探[J]. 数码世界, 2020: 68-69.

[8]郑明秋, 蒙连超, 赵海侠. MySQL数据库实用教程[M].北京理工大学出版社, 2019: 4.

[9]胡巧儿.MySQL数据库原理与应用项目化教程微课版[M].电子工业出版社.2021:74-79.

[10]周小娟.基于springboot框架与XML技术的工业锅炉智能化监控系统设计[J].工业加热,2020,49(12):31-34.

[11]沈蕴梅. 电子商务网站建设springboot+MySQL项目开发教程[M]. 北京:北京理工大学出版社, 2019:95-102.

[12]向桂玲.XML数据库强制访问控制策略探讨[J].信息与电脑,2021,34(04):186-188.

[13]Vanier Eric, Malepati Tejaswi, Shah Birju. Advanced MySQL 8[M]. Packt Publishing, 2019: 89-95.

[14]Kromann. springboot and MySQL Recipes[M]. Apress, 2020:20-36.

[15]AlDwairi Mahmoud,Shatnawi Ahmed S.,AlKhaleel Osama,AlDuwairi Basheer. Ransomware-Resilient Self-Healing XML Documents[J]. Future Interspringboot,2021,14(4).

致 谢

时光飞逝,转眼间四年的大学就要过去了。当我做到了大学里最后任务的最后一个模块时,我意识到自己将要毕业了,将离开陪伴了自己四年快乐时光的校园。回想起在学校的四年,让我有很深的感触。回想起在学校的点点滴滴,让我有太多无法忘记的人和事。学校的室友,同学,朋友,老师,图书馆,教学楼等,当这些东西在我脑里闪过的时候,我的心里很不是滋味。

首先,我要感谢我的亲人。他们无论何时都是我最亲近的人,无论我对他们怎么发脾气,他们都不会生我的气。每次当我因为某些事而无法承受的时候,他们总是会第一时间来关心我,来给我出主意,帮我度过难关。今后,我也会努力前进,回报我的亲人们对我的支持。

当然,还要感谢我的毕设指导老师。他是一位发自内心希望我们以后能功成名的老师。他陪伴了我几乎整个大学时光,他每次上课的时候都会向我们分享他所做过的程序。将他自己的实战经验授予我们。他会将自己觉的最有用的东西交给我们,还会向我们分享他觉得非常实用的软件,如果我们无法下载,他也会帮我们下载软件。记得在大四上学期的时候,他还帮助我们重装系统,给我们安装最实用的软件。他也是一个非常有责任感的老师,他会经常询问我们的论文情况,如果我们有问题,他都会在第一时间给我们解答。或许对于一位老师来讲,学生学有所成是他的期望。

还要感谢我的室友们。虽然这几年的生活会有磕磕绊绊,但是每次我有困难或者不开心的时候,他们都会给我建议,让我不在难过。每当我过生日的时候,他们都会不约而同的为我庆祝。每当我有困难的时候,他们总是站在我这一边,为我考虑。而在和他们沟通后,我都会从坏心情里走出来,变的愉悦。所以,我也很感谢他们这四年的陪伴。

时光飞逝,四年大学生活转眼间就要过去了。这一刻,四年里的时光又在我的脑海里进行了一遍。我的室友,同学,老师,这一刻,我已止不住自己的泪水。我有太多的回忆永远的刻在了脑子里,我不会忘记他们,不会忘记和他们的点点滴滴。于此同时,我会积极备战考研,吸取第一次的失败经验,争取再二战中取得一个好的成绩,考上心目中理想的学校。我一定会加油的!