网站管理助手ftp新型网站建设

自学python如何成为大佬(目录):https://blog.csdn.net/weixin_67859959/article/details/139049996?spm=1001.2014.3001.5501

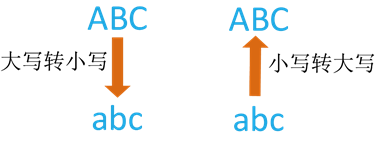

在Python中,字符串对象提供了lower()方法和upper()方法进行字母的大小写转换,即可用于将大写字母转换为小写字母或者将小写字母转换为大写字母,如图10所示。

图10 字母大小写转换示意图

(1)lower()方法

lower()方法用于将字符串中的大写字母转换为小写字母。如果字符串中没有需要被转换的字符,则将原字符串返回;否则将返回一个新的字符串,将原字符串中每个需要进行小写转换的字符都转换成等价的小写字符。字符长度与原字符长度相同。lower()方法的语法格式如下:

str.lower()

其中,str为要进行转换的字符串。

例如,使用lower()方法后,下面定义的字符串将全部显示为小写字母。

str1 = 'WWW.Mingrisoft.com'

print('原字符串:',str1)

print('新字符串:',str1.lower()) # 全部转换为小写字母输出

(2)upper()方法

upper()方法用于将字符串中的小写字母转换为大写字母。如果字符串中没有需要被转换的字符,则将原字符串返回;否则返回一个新字符串,将原字符串中每个需要进行大写转换的字符都转换成等价的大写字符。新字符长度与原字符长度相同。upper()方法的语法格式如下:

str.upper()

其中,str为要进行转换的字符串。

例如,使用upper()方法后,下面定义的字符串将全部显示为大写字母。

str1 = 'WWW.Mingrisoft.com'

print('原字符串:',str1)

print('新字符串:',str1.upper()) # 全部转换为大写字母输出

场景模拟:在明日学院的会员注册模块中,要求会员名必须是唯一的,并且不区分字母的大小写,即mr和MR被认为是同一用户。

![]()

实例05 不区分大小写验证会员名是否唯一

在IDLE中创建一个名称为checkusername.py的文件,然后在该文件中定义一个字符串,内容为已经注册的会员名称,以“|”进行分隔,然后使用lower()方法将字符串全部转换为小写字母,接下来再应用input()函数从键盘获取一个输入的注册名称,也将其全部转换为小写字母,再应用if…else语句和in关键字判断转换后的会员名是否存在转换后的会员名称字符串中,并输出不同的判断结果,代码如下:

# 假设已经注册的会员名称保存在一个字符串中,以“|”进行分隔

username_1 = '|MingRi|mr|mingrisoft|WGH|MRSoft|'

username_2 =username_1.lower() # 将会员名称字符串全部转换为小写

regname_1 = input('输入要注册的会员名称:')

regname_2 = '|' + regname_1.lower() + '|' # 将要注册的会员名称全部转换为小写

if regname_2 in username_2: # 判断输入的会员名称是否存在

print('会员名',regname_1,'已经存在!')

else:

print('会员名',regname_1,'可以注册!')

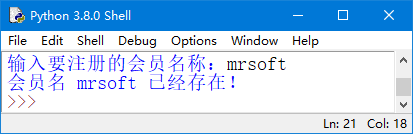

运行实例,输入mrsoft后,将显示如图11所示的结果;输入python,将显示如图12所示的结果。

图11 输入的名称已经注册

图12 输入的名称可以注册