佛山网站开发哪家好信融网站建设网站开发

🍅 点击文末小卡片,免费获取软件测试全套资料,资料在手,涨薪更快

全局变量和环境变量

全局变量:在postman全局生效的变量,全局唯一

环境变量:在特定环境下生效的变量,本环境内唯一

设置:

全局变量:

pm.globals.set("variable_key", "variable_value1");环境变量:

pm.environment.set("variable_key", "variable_value2");

获取:

全局变量:

1、代码获取

var gl = pm.globals.get("variable_key"); // gl的值为variable_value1

2、请求参数获取 {{variable_key}}

环境变量:

1、代码获取

var en = pm.environment.get("variable_key"); // en的值为variable_value2

2、请求参数获取 {{variable_key}}

实现接口关联

1、json提取器

// 把返回的字符串格式的数据转化为json格式

var result = json.parse(responseBody);// 通过json对象取value值 result.token

// 把取得的result设置为全局变量pm.globals.set("token", result.token); // 为全局变量后,可以通过---获取全量变量,实现关联

{{token}} 或 pm.globals.get("token");

2、正则表达式提取器

// match匹配

var result = responseBody.match(new RegExp(' "token":"(.*?)" '));// 设置为全局变量 result[1] (下标为1的值为想要的token值)

pm.globals.set("token", result[1]); // 为全局变量后,可以通过---获取全量变量,实现关联

{{token}} 或 pm.globals.get("token");

加密、解密、内置/自定义动态参数

1、对称的加密方式(私钥加密)

Base64加密:

// 转为UTF-8编码格式

var username = CryptoJS.enc.utf-8.parse(''admin'');// 转为base64加密

var base64_username = CryptoJS.enc.Base64.stringify(username );console.log(base64_username); // YWRtaW4K

Base64解密:

// 先解密

var username = CryptoJS.enc.Base64.parse(YWRtaW4K);// 解密后转为utf-8格式

var new_username = username.tostring(CryptoJS.enc.utf-8);console.log(new_username); // admin

2、非对称式加密方式(双钥加密) :

RSA加密方式:

由一个密码生成公钥和私钥,公钥加密、私钥解密;私钥加密、公钥解密

3、只加密不解密

MD5 、SHA系列

// MD5加密

var password = CryptoJS.MD5("admin").tostring().toUpperCase(); // 选择32位大写

postman的内置动态参数:

{{$timestamp}} //自动生成当前时间的时间戳 (不方便做断言){{$randomInt}} //生成0-1000的随机数 {{$guid}} //生成一个GUID长字符串随机数

自定义参数:

自定义时间戳的参数

// 获取当前系统时间

var times = Date.now();// 把获取的时间设置为全局变量

pm.globals.set("times", times); // 使用{{times}}即可

动态参数断言:

在postman的tests页签,不能通过{{}}方式获取全局变量,只能通过以下方式获取

①获取全局变量的方式,拼接 pm.globals.get(“times”)

②globals[“times”]

③globals.times

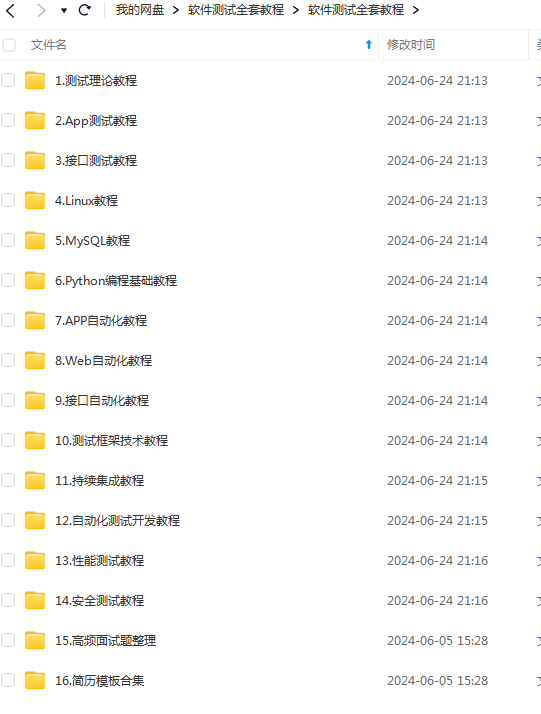

最后感谢每一个认真阅读我文章的人,礼尚往来总是要有的,虽然不是什么很值钱的东西,如果你用得到的话可以直接拿走:

这些资料,对于做【软件测试】的朋友来说应该是最全面最完整的备战仓库,这个仓库也陪伴我走过了最艰难的路程,希望也能帮助到你!凡事要趁早,特别是技术行业,一定要提升技术功底。