搜狗站长平台主动提交成都系统软件定制开发

配置文件路径

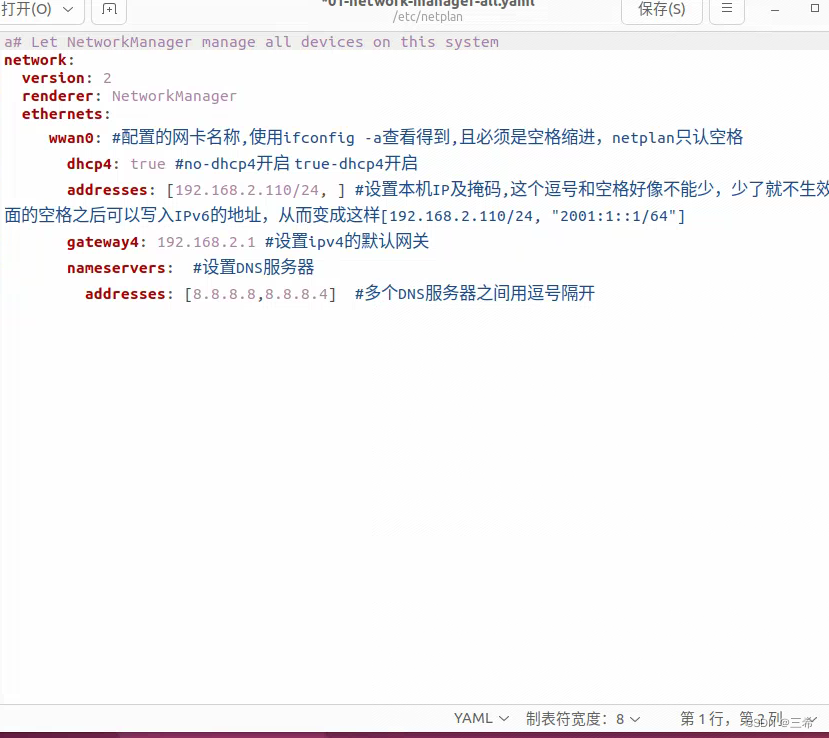

在Ubuntu中,网络配置文件通常位于/etc/netplan/目录下,其文件名以.yaml为后缀。Netplan是Ubuntu 17.10及更高版本中默认的网络配置工具,用于配置网络接口、IP地址、网关、DNS服务器等。

我们可以看到配置文件为 01-network-manager-all.yaml

编辑配置文件

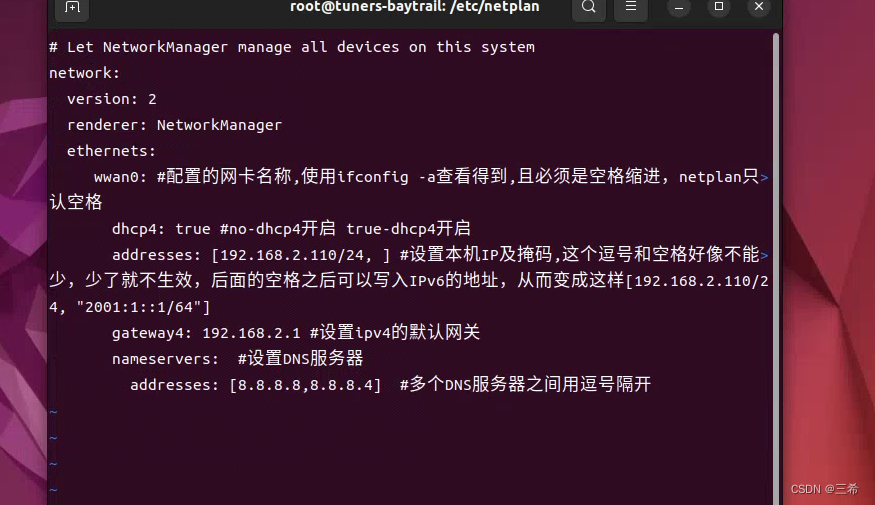

输入编辑命令:该命令必须是有系统界面的,终端编辑的话需要用另一个命令

有操作系统界面

gedit 01-network-manager-all.yaml

![]()

修改好直接保存

终端执行(无操作系统界面)

vi 01-network-manager-all.yaml

生效

sudo netplan apply