企业网站群建设模式郁金香导航 汕头大学网址大全

查看提交历史

1 git log

撤消操作

任何时候,你都有可能需要撤消刚才所做的某些操作。接下来,我们会介绍一些基本的撤消操作相关的命令。请注意,有些操作并不总是可以撤消的,所以请务必谨慎小心,一旦失误,就有可能丢失部分工作成果。

修改最后一次提交

1 git commit --amend

如果刚才提交时忘了暂存某些修改,可以先补上暂存操作,然后再运行--amend 提交。,第二个提交命令会修正了第一个的提交内容。

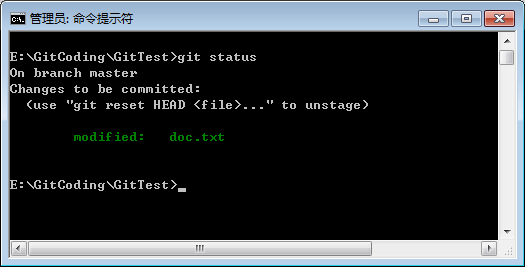

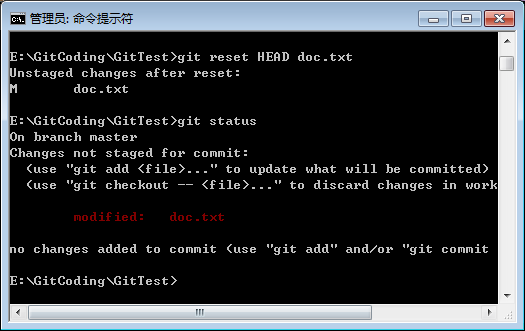

取消已经暂存的文件

接下来的两个小节将演示如何取消暂存区域中的文件,以及如何取消工作目录中已修改的文件。不用担心,查看文件状态的时候就提示了该如何撤消,所以不需要死记硬背。

取消前状态:

取消后状态:

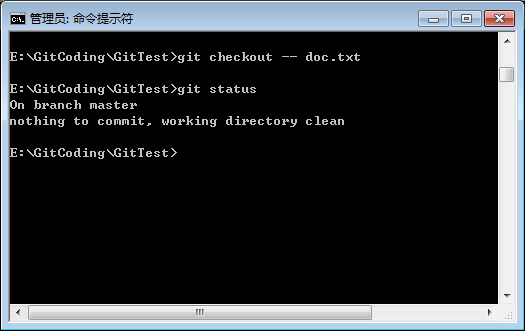

取消对文件的修改

记住,任何已经提交到Git 的都可以被恢复。即便在已经删除的分支中的提交,或者用--amend 重新改写的提交,都可以被恢复(关于数据恢复的内容见第九章)。所以,你可能失去的数据,仅限于没有提交过的,对Git 来说它们就像从未存在过一样。