网站开发主管工作内容做视频剪辑接私活的网站

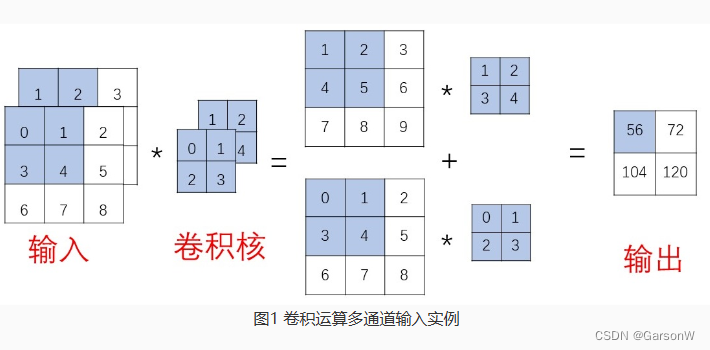

多通道输入

当输入的数据包含多个通道时,我们需要构造一个与输入通道数相同通道数的卷积核,从而能够和输入数据做卷积运算。 假设输入的形状为n∗n,通道数为ci,卷积核的形状为f∗f,此时,每一个输入通道都应该分配一个形状为f∗f的卷积核,所以卷积核的形状可以表示为ci∗f∗f。

从上图的实例中可以看出,多通道输入的计算方法就是单独计算每个通道中卷积的结果,再将不同通道得到的结果对应相加到一个通道,得到输出的结果。

多通道输出

当输入通道有多个时,我们增加了卷积核的通道数,并对结果进行了累加,这样不论输入通道数为多少,输出通道数都为1。所以如果我们需要增加输出的通道,就可以增加多个多通道的卷积核,每一个多通道的卷积核可以获得一个通道的输出,这样就可以获得多通道输出了。 假设卷积核的输入通道数和输出通道数分别为ci和co,如果想要得到含多个通道的的输出,我们可以为每个输出分别创建一个形状为ci∗f∗f的卷积核,然后在输出通道上将结果连接起来,就可以得到多通道的输出,最终卷积核的形状就是co∗ci∗f∗f。

如何调用 Pytorch 中的多通道输入和输出

nn.Conv2d()中的参数in_channels,out_channels就是用于控制卷积层的输入通道数和输出通道数。

nn.Conv2d(1, 6, 5) # in_channels, out_channels, kernel_size上方这个示例中就定义了最简单的卷积层,其中in_channels=1,out_channels=6。

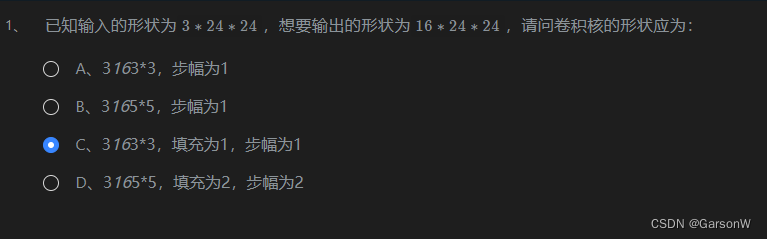

习题

因为输出ci输入co分别为3、10,所以卷积核的深度为3x10,卷积核的w和h需要根据步幅和填充确定。已知输入输出形状wh不变,由公式 (n-f+2p)/s+1 = n 得到(24 - 3 + 1*2)/1 + 1 = 24 与c选项一致