php网站欣赏wordpress搜索页面不同

文章目录

- 1.案例

- 1.1 原始案例

- 1.2 改进一:类上遵循单一职责原则

- 1.3 改进二:方法上遵循单一职责原则

- 2.小结

1.案例

1.1 原始案例

package com.sdnu.principle.singleresponsibility;

//客户端

public class singleResponsibility {public static void main(String[] args) {Vehicle vehicle = new Vehicle();vehicle.run("汽车");vehicle.run("卡车");}

}

//交通工具

class Vehicle{public void run(String vehicle){System.out.println(vehicle + "在公路上跑");}

}

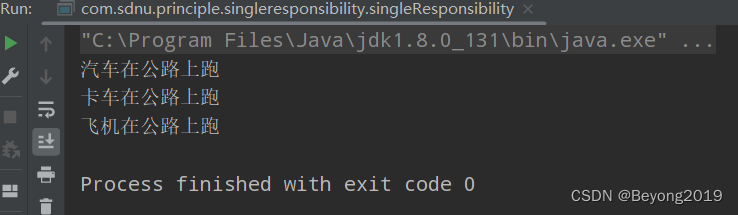

假如现在来了一架飞机,我们不可能让飞机在公路上跑吧,如下:

package com.sdnu.principle.singleresponsibility;

//客户端

public class singleResponsibility {public static void main(String[] args) {Vehicle vehicle = new Vehicle();vehicle.run("汽车");vehicle.run("卡车");vehicle.run("飞机");}

}

//交通工具

class Vehicle{public void run(String vehicle){System.out.println(vehicle + "在公路上跑");}

}

显然不符合常理。显然违反单一职责原则。

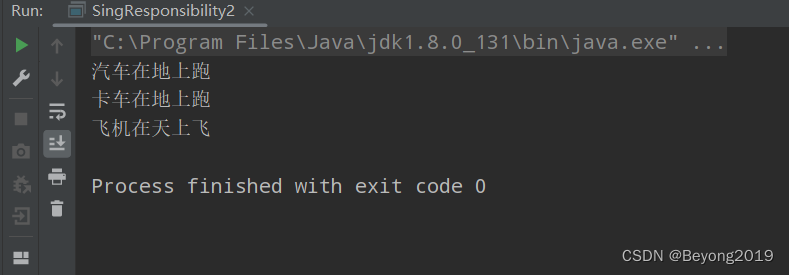

1.2 改进一:类上遵循单一职责原则

package com.sdnu.principle.singleresponsibility;

//客户端

public class SingResponsibility2 {public static void main(String[] args) {RoadVehicle roadVehicle = new RoadVehicle();roadVehicle.run("汽车");roadVehicle.run("卡车");AirVehicle airVehicle = new AirVehicle();airVehicle.run("飞机");}

}class RoadVehicle{public void run(String vehicle){System.out.println(vehicle + "在地上跑");}

}class AirVehicle{public void run(String vehicle){System.out.println(vehicle + "在天上飞");}

}

我们对类进行了分解,这样做虽然符合了类上单一职责原则,但是需要修改太多东西了,而且需要修改客户端。

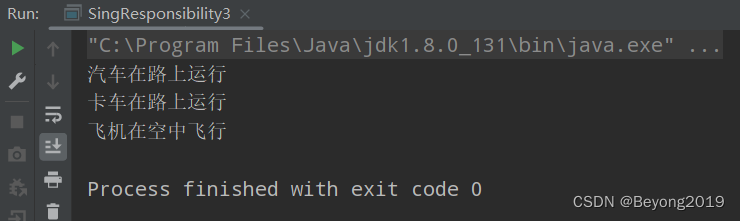

1.3 改进二:方法上遵循单一职责原则

package com.sdnu.principle.singleresponsibility;public class SingResponsibility3 {public static void main(String[] args) {Vehicle3 vehicle = new Vehicle3();vehicle.runOnRoad("汽车");vehicle.runOnRoad("卡车");vehicle.runOnAir("飞机");}

}class Vehicle3{public void runOnRoad(String vehicle){System.out.println(vehicle + "在路上运行");}public void runOnAir(String vehicle){System.out.println(vehicle + "在空中飞行");}

}

这种方法虽然没有在类上遵循单一职责原则,但是在方法上遵循了单一职责原则。并且改动很小,只需要在Vehicle中添加一个方法而已。(严格来说没有遵循单一职责原则)

2.小结

(1) 注意标准的单一职责原则是在类级别上

(2)注意事项:

- 降低类的复杂程度,一个类只负责一个职责。

- 提高类的可读性,可维护性。

- 降低变更引起的风险。

- 通常情况下,我们应该遵循单一职责原则,只有逻辑足够简单,才可以在代码级别上违法单一职责原则。只有类中的方法数量足够少,才可以在方法级别上保持单一职责原则。

(3)核心:单一职责原则的实际上是一个类应该只负责一项职责,以此控制类的粒度大小、将对象解耦、提高其内聚性,但是对于粒度的大小需要有经验的开发者自己把握。