网站没有权重苏州网站建设找思创

超硬材料是指硬度特别高的材料,可分为天然以及人造两种,前者主要包括天然的钻石(金刚石)、黑钻石,后者则包括人造金刚石、立方氮化硼。

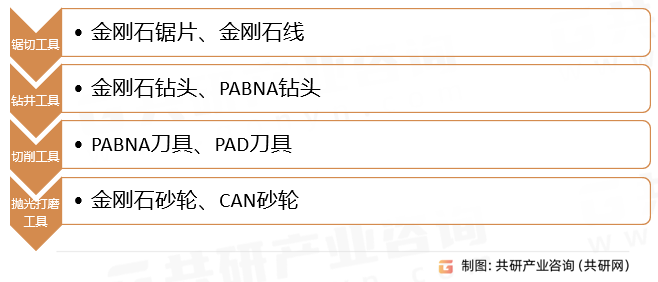

超硬材料制品分类

资料来源:共研产业咨询(共研网)

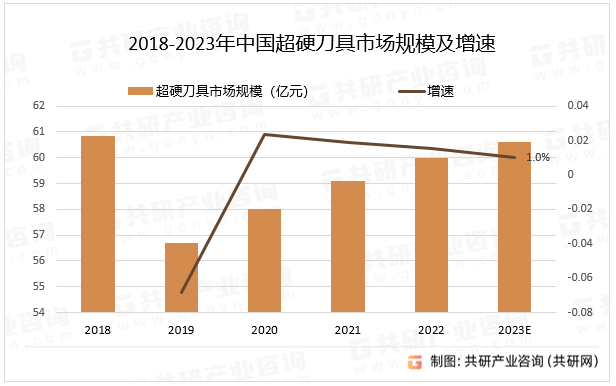

2023-2029年中国超硬材料制品行业市场供需态势及发展战略咨询报告中显示:超硬材料应用极为广泛,市场需求总体保持稳定增长。随着我国的高端制造业持续发展,PCBN刀具、金刚石线、金刚石钻头等为代表的超硬材料制品需求持续增长,在集成电路、光伏、精密制造等领域的应用程度持续加深,其中2022年中国超硬刀具市场规模同比增长1.5%。

2018-2023年中国超硬刀具市场规模及增速

资料来源:共研产业咨询(共研网)

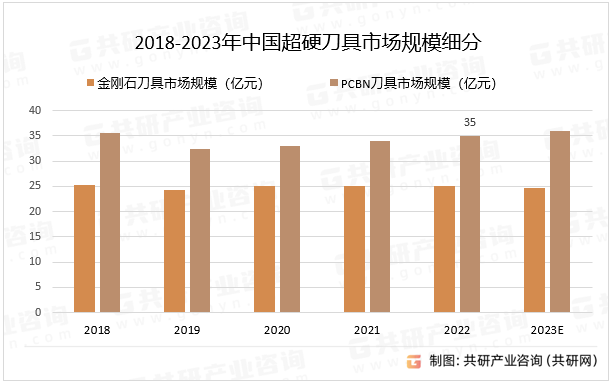

超硬材料广泛应用于机械、冶金、地质、石油、煤炭、石材、木材、建筑、汽车、家电等传统领域,电子信息、航天航空、国防军工等高技术领域,其中2022年中国金刚石刀具市场规模同比下降0.4%;PCBN刀具市场规模同比增长2.9%。

2018-2023年中国超硬刀具市场规模细分

资料来源:共研产业咨询(共研网)