太仓网站建设服务网站建设学多长时间

用龙梦迷你电脑福珑2.0上做web服务器是可行的。已将一个网站源码放到该电脑,在局域网里可以访问网站网页。另外通过在同一局域网内的一台windows10电脑上安装花生壳软件,也可以在外网访问该内网服务器网站网页。该电脑的操作系统属于LAMP。在该电脑上安装了Loongnix 1.0 。该操作系统默认安装了Apache2.4,php5.6。修改好软件源以后,能顺利安装web服务器所需要的软件mysql(mariadb10.0)。详情请查看我写的上一篇文章:在龙梦迷你电脑福珑2.0上试了三个操作系统。

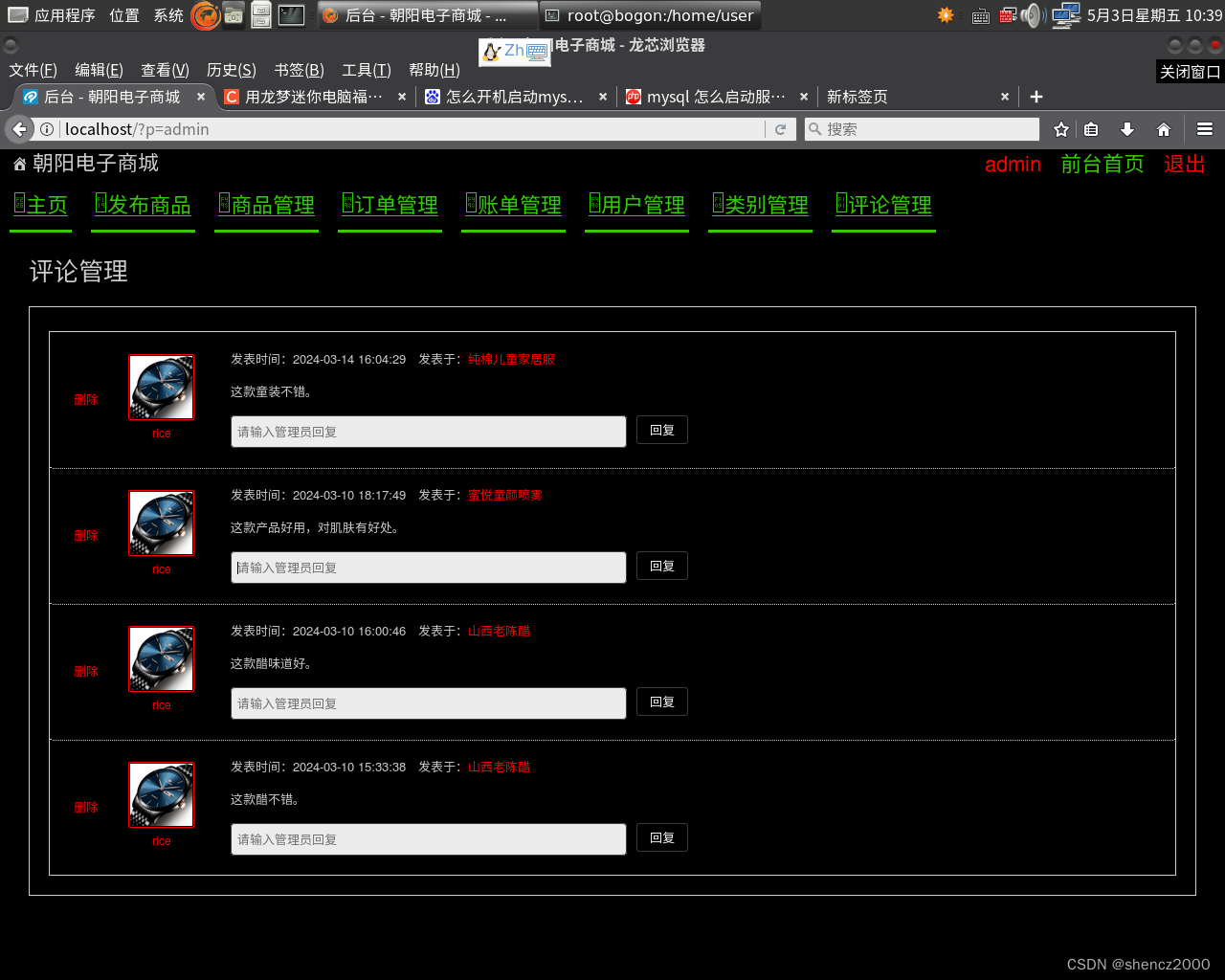

下面放几张图片。